## A THESIS ON

#### IRON RELATED DEFECTS IN QUENCHED SILICON

## SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENT

## Master of Philosophy

In Physics By

## Muhammad Nawaz

2005

Department of Physics Quaid-i-Azam University Islamabad, Pakistan

## CERTIFICATE

Certified that the work reported in this thesis has been carried out in Advance Materials Physics Laboratory by **Muhammad Nawaz Saleh** under my supervision.

Archan

Prof. Dr. Akbar Ali

Professor of Physics Advance Materials Physics Laboratory Department of Physics Quaid-i-Azam University Islamabad, Pakistan

Submitted through Prof. Dr. M. Aslam Baig

Prof. Dr. M. Aslam Baig Chairman Department of Physics Quaid-i-Azam University Islamabad, Pakistan

## DEDICATED TO

"Beginning of a Love Poem & To The End of Fairy Tales"

م اردست الني عين سرايس معولوں كوجن يرشحف دار ف شب انتخاب كى One not to get it, what is desired. Other to get it.

#### ACKNOWLEDGEMENT

All praise be to Almighty ALLAH, Lord of the Worlds. He Who is the Absolute Creator, the Cherisher and Sustainer of the Worlds. Thee Who is to be Worshiped. There is no partner in His creation, deed, and order. Hazrat Muhammad (saas) is His last messenger to all mankind. Almighty Allah Who is the source of all knowledge and wisdom endowed to mankind, and the Holly Prophet Muhammad (saas) who is forever a torch of guidance for humanity as a whole. Million of Darrod and Salams on our beloved Hazrat Muhammad (saas). Allah has bestowed me courage and health to accomplish this research work in time.

I am deeply indebted to my supervisor Prof. Dr. Akbar Ali who has been a constant source of guidance and encouragement for me throughout this research work. He helped and provided me every thing in the development of our home made digital computerized DLTS system. He taught me the art of research.

I acknowledge Semiconductor Physics for extending cooperation, help, encouragement, and facilitating me in solving different problems.

I would like to thank Prof. Dr. Muhammad Aslam Baig chairman department of Physics for extending his support and providing all needed facilities for lab. and this research work.

The contribution of Mr. Aamar Khan Jaddon for helping in programming of software is highly appreciable. He spent many nights for solution of problems related to coding of software. His help and valuable discussion led me to complete this research project in time. I am also thankful to Mr. Sohail Ahmad for his assistance in solving problems related to the internal clock of the computer. This is one of the major problems of the programming. One has to use minimum sources of internal clock for better programming.

I am grateful to Mr. Ghulam Nabi for providing computer accessories. Without his help I could not do hardware of system. I also thanks to my lab. follow Mr. Abdul Majid and Mr. Muddassar Rafiqe.Two friends, Mr. M. Mazhar Kalyar & Manzoor Ellahi can not be neglected for their company in the lonely nights of research. I am thankful to Pakistan Science Foundation (PSF) for providing me financial assistance to execute this project.

Last but most of important thanks go to my family because they have scarified their lives for my life. It is all due to them where today I am. I am their dreams. Allah bless them happiness, health, peace of life, and success in this world and Hereafter. (Amin)

Muhammad Nawaz

#### ABSTRACT

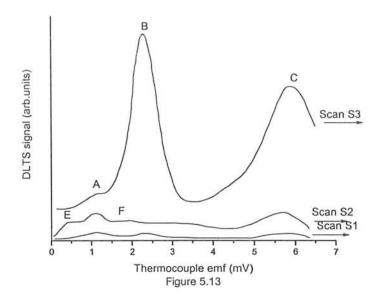

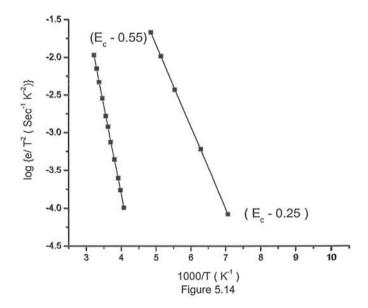

The aim of our research project is to (i) develop a digital computerized DLTS system in the laboratory and (ii) study iron related defects in quenched silicon. In the first part of project, two main IEEE based components, capacitance meter and pulse generator are interfaced with a computer. A software in Visual C++ has been programmed for communication and acquisition of data. Preliminary test run using our DLTS system has been taken to establish the performance of the system. It is found that our system is working well so for as the test run and initial measurements are concerned. However improvement in software and supporting equipment is still needed to enhance and extend its working. In the second part of the project, quenched samples of silicon has been studied in detail using a commercial DLTS system available in the department. At least two deep levels at energies Ec-0.55, and Ec-0.25 eV are observed in high concentration. The annealing characteristics of the two states  $E_c$ -0.55 and  $E_c$ -0.25 eV were measured. The annealing characteristics of Ec-0.55 gold related acceptor level showed the contribution of signal due to iron in a peak corresponding to energy position Ec- 0.55 eV. The other energy state at  $E_c$ -0.25 eV is identified as iron-gold complex. The characteristics of these two defects also suggest that they are pinned together. The comparison of emission rate signatures and annealing characteristics revealed that energy state at E<sub>c</sub>-0.55 eV is due to gold acceptor and energy state E<sub>c</sub>-0.25 eV is due to iron-gold complex. The inadvertent gold and iron are present in the samples.

## CONTENTS

#### CHAPTER 1

#### INTRODUCTION

| 1.1   | Introduction                                | 1 |

|-------|---------------------------------------------|---|

| 1.2   | Classification of Defects in Semiconductors | 2 |

| 1.2.1 | Shallow Level Defects                       | 3 |

| 1.2.2 | Deep Level Defects                          | 3 |

| 1.3   | Motivation of Present Work                  | 4 |

| 1.4   | Scheme of Thesis                            | 4 |

|       | References                                  | 5 |

#### CHAPTER 2

#### HISTORICAL REVIEW OF IRON RELATED DEFECTS IN

#### SILICON

| 2.1 | Introduction  | 6  |

|-----|---------------|----|

| 2.2 | Brief History | 7  |

|     | References    | 12 |

#### CHAPTER 3

## PHYSICS OF $P^{\scriptscriptstyle +}n$ JUNCTION & ELECTRICAL TECHNIQUES

| 3.1 | Current-Voltage Characteristics     | 14 |

|-----|-------------------------------------|----|

| 3.2 | Capacitance-Voltage Characteristics | 16 |

| 3.3 | Single-Shot Transient Technique     | 19 |

| 3.4 | Deep Level Transient Spectroscopy   | 22 |

| 3.5 | DLTS Measurements Procedure         | 23 |

| 3.6 | Deep Level Defect Characteristics   | 28 |

| 3.7 | Thermal Emission Rate               | 28 |

| 3.8 | Thermal Activation Energy           | 29 |

| 3.9  | Deep Level Concentration | 30 |

|------|--------------------------|----|

| 3.10 | Capture Cross-Section    | 32 |

|      | References               | 33 |

| D   | DEVEL  | OPMENT OF DIGITL COMPUTERIZED "DLTS" S   | YSTEM |

|-----|--------|------------------------------------------|-------|

| 4.1 | Introd | luction                                  | 35    |

| 4.2 | Theor  | y of Continuous Time Averaging Technique | 36    |

| 4.3 | Analo  | g Methods                                | 37    |

|     | 4.3.1  | Advantages of Analog Methods             | 37    |

|     | 4.3.2  | Disadvantages of Analog Methods          | 38    |

| 4.4 | Digita | l Methods                                | 38    |

|     | 4.4.1  | Advantages of Digital Methods            | 38    |

|     | 4.4.2  | Disadvantages of Digital Methods         | 38    |

| 4.5 | Hardw  | vare of Digital computerized DLTS System | 39    |

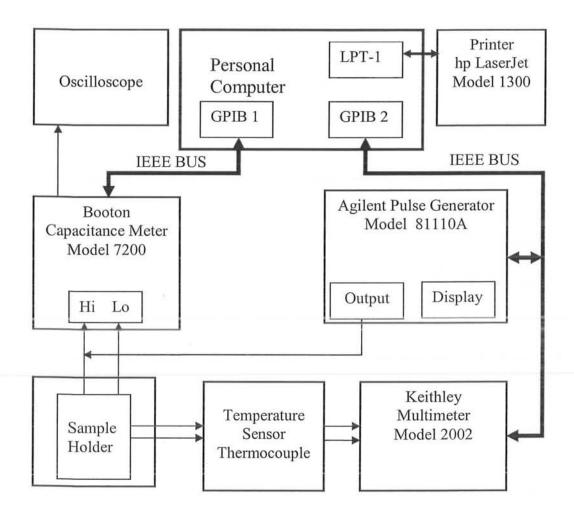

|     | 4.5.1  | Boonton Capacitance Meter                | 40    |

|     | 4.5.2  | Pulse Generator                          | 41    |

|     | 4.5.3  | Digital Multimeter                       | 41    |

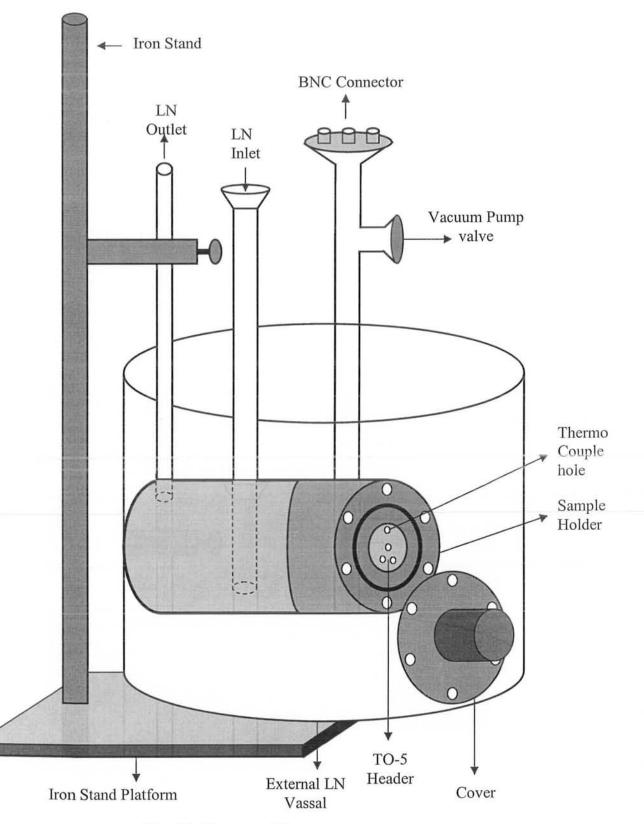

|     | 4.5.4  | Cryostat                                 | 42    |

|     | 4.5.5  | Interfacing Units                        | 42    |

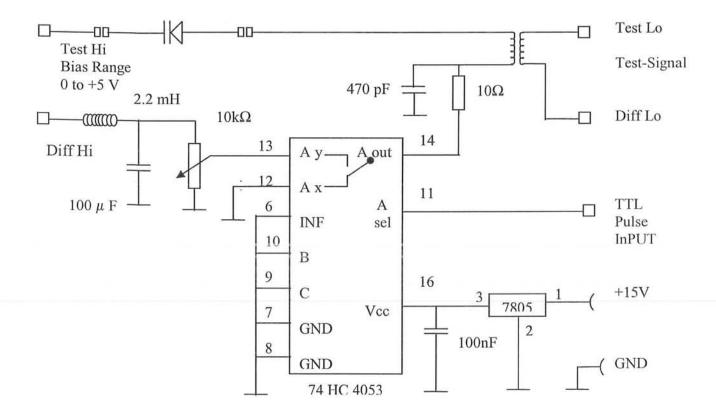

|     | 4.5.6  | Coupling Circuit                         | 45    |

| 4.6 | Softw  | are of Digital Computerized DLTS System  | 47    |

|     | 4.6.1  | Introduction                             | 47    |

|     | 4.6.2  | Communicating With a Single GPIB Device  | 47    |

|     | 4.6.3  | Communicating With Multiple GPIB Devices | 48    |

|     | 4.6.4  | Global Status Variables                  | 48    |

|     | 4.6.5  | Rate Window                              | 52    |

| 4.7 | Main   | Control Pannel                           | 52    |

|     | 4.7.1  | External Bias Parameters Panel           | 52    |

|     | 4.7.2  | Capacitance Meter Bus Mnemonics Panel    | 53    |

| 4.7.3      | Temperature Control Panel | 54 |

|------------|---------------------------|----|

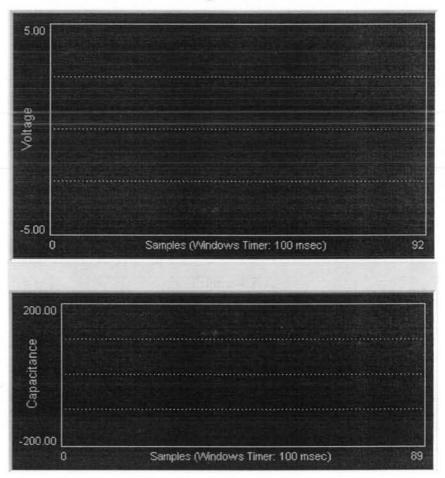

| 4.7.4      | Display Panel             | 54 |

| References |                           | 56 |

| EXPERIMENTAL DE | TAILS | , |

|-----------------|-------|---|

|-----------------|-------|---|

| 5.1   | Introduction       |                                                      | 58 |

|-------|--------------------|------------------------------------------------------|----|

| 5.2   | Sample Preparation |                                                      | 58 |

| 5.3   | Curr               | ent-Voltage (I-V) Measurements                       | 59 |

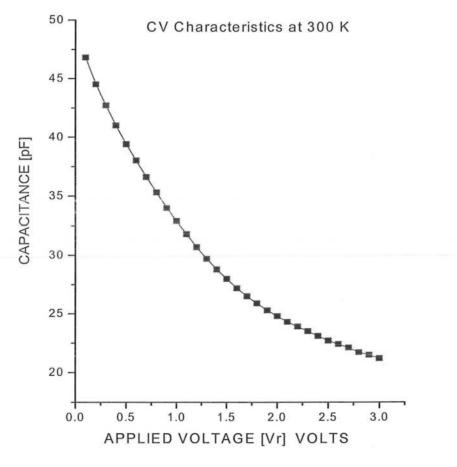

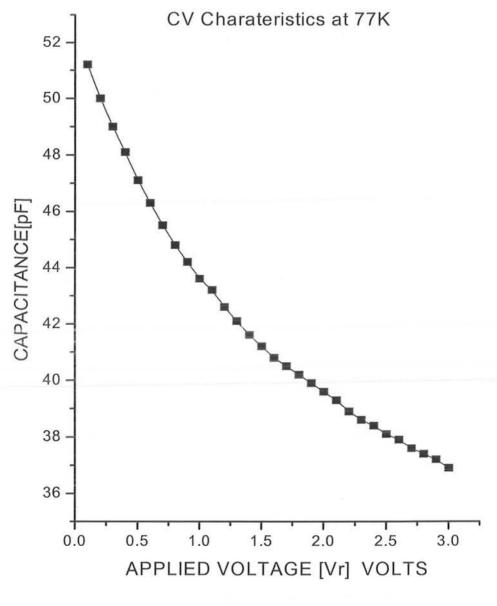

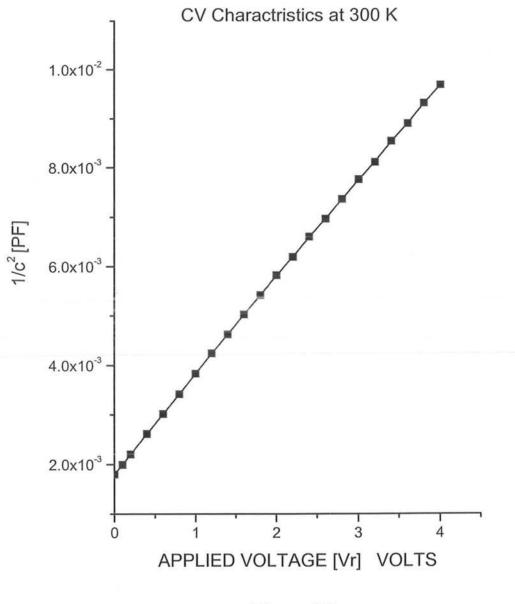

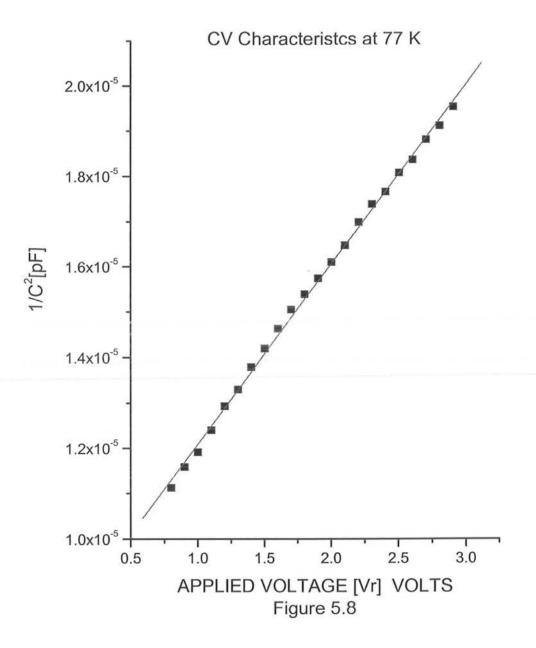

| 5.4   | Capa               | citance –Voltage (C-V) Measurements                  | 65 |

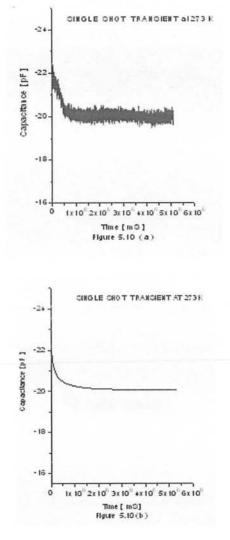

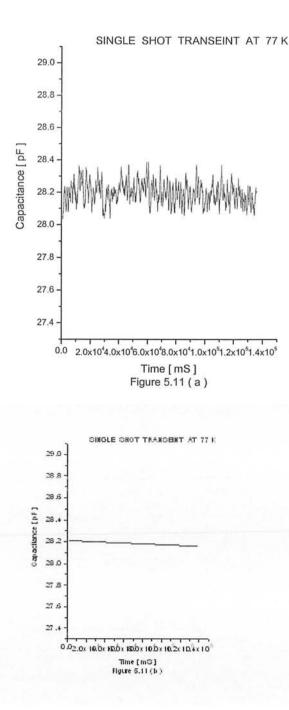

| 5.5   | Sing               | le-Shot Measurements                                 | 70 |

| 5.6   | DLT                | S Measurements                                       | 73 |

| 5.7   | Meas               | surements Using Company Made DLTS                    | 75 |

|       | 5.7.1              | Virgin Sample                                        | 75 |

|       | 5.7.2              | Air Quenched Samples                                 | 76 |

| 5.8   | Compa              | arison of Samples Quenched in Air With Virgin Sample | 76 |

| 5.9   | Emissi             | on Rate Measurements                                 | 77 |

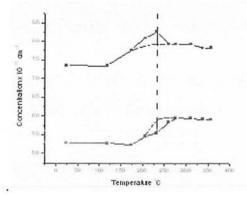

| 5.10  | Isochro            | onal Annealing                                       | 77 |

| 5.11  | Discu              | ssion                                                | 78 |

|       | 5.11.1             | Thermally Induced Deep Level C                       | 78 |

|       | 5.11.2             | Thermally Induced Deep Level B                       | 79 |

| 5.12  | Conclu             | ision                                                | 80 |

| 5.13  | Work               | Suggested for Future                                 | 80 |

|       | Refere             | nces                                                 | 82 |

| Gloss | sary               |                                                      | 83 |

| Table | e 1                |                                                      | 89 |

| Table | e 2                |                                                      | 90 |

1

## Introduction

#### 1.1 Introduction

Semiconductors are the most significant materials because the whole modern electronic technology is based on them. Semiconductors are the main focus of research since last fifty years. They are very useful because of their temperature depended electrical conductivity. They overpass the large breach of electrical conductivities between metals and insulators. Their electronic properties can be controlled by applying voltage, magnetic field, light, mechanical stress, and change in temperature [1].

Today the modern semiconductor electronic devices are playing an important role in almost every field of life extending from domestic appliances to the sophisticated devices used in defense and space technology. Developments in the device technology have brought revolution in the field of high speed communication, computation, microminiaturization of integrated circuitry and fabrication of the novel nanostructures. An increasing variety of materials is being used to produce semiconducting devices to perform specific device functions. Considerable efforts are being made to increase efficiency and to reduce the dimensions of the devices to produce

1

low cost devices. Silicon, because of its great abundance in earth's crust and many useful properties, is still dominantly the material of choice in the semiconductor industry.

Crystal defects play a predominant role in controlling the most interesting properties of semiconductors. As donors and acceptors, they find out the electronic properties of the semiconducting material. Defects in semiconductors have retained a central role, from the invention of the transistor to the current generation of microelectronic devices and circuits. The central role, adverse or beneficial, has been the main thrust in advancing methods and techniques for the understanding of the origin of defects, their characteristics and influence on device performance. Thus, the remarkable advances in solid state electronic science and technology are to a large extent directly attributable to the role of defects in semiconductors. Similarly, the function of electronic devices which manipulate, amplify, switch and control currents, voltages, process and store information, is essentially based on the transition of electron from one energy state to other which are due to controlled introduction of defects in semiconductor crystal.

#### 1.2 Classification of Defects in Semiconductors.

Impurities and structural defects in semiconductor crystals introduce energy states within the forbidden energy gap. If an atom of host lattice is replaced by a different atom that belongs to some other group of the period table, it changes the periodic potential of the crystal and the wave function at that site. New electronic states are produced by such a defect whose energy may lie within the band gap. These levels can be classified into the following two categories depending upon the depth of the energy level corresponding to the ground state of the impurity with respect to the nearest band edge.

- Shallow level defects

- Deep-level defects

#### 1.2.1 Shallow level Defects

The defects states produced in the band gap closer to either the conduction or the valence band edges are named as shallow level defects. If the wave function describing

the defect state in the band structure of the host crystal is delocalized in real space, the state is known as shallow level [2-3].

Shallow levels have small binding energies (typically << 0.1eV). Shallow levels act as either donors or acceptors and contribute electrons or holes respectively. They determine the conduction properties of the semiconductors and are mostly ionized at room temperature. When impurities from group IIIA and group VA of the periodic table are introduced into group IVA elements then energy levels close to the valence- and conduction-band edges are produced.

#### 1.2.2 Deep-Level Defects.

If the binding energy of the defects is large than shallow levels from the nearest band edge, it is called a deep level and the defect is termed as a deep level defects. If the wave function is localized in real space the defect state introduces a deep level [2-3]. The importance of the deep level defects lies in their property to act as a mediating step within the band gap during the transition of electrons and holes and hence to control their lifetime. They are commonly caused by impurities, device processing steps and irradiation with high energy particles. For example, impurities from groups other than III and V of the periodic table such as copper, iron, and gold etc. introduce energy levels nearer to the middle of the forbidden energy gap. Deep-levels defects have enormous impact on the performance of electronic devices and play a key role in controlling the minority carrier-life time.

#### 1.3 Motivation of Present Work.

Tremendous and enormous progress in silicon technology has motivated me to investigate the iron contamination in silicon materials. This marvelous advancement in silicon technology has become only possible because of the reduction of iron contamination during the growth processes of the device. The Semiconductor Industry Association (SIA) International Technology Roadmap specified  $1.4 \times 10^{10}$  cm<sup>-2</sup> as the maximum allowable surface iron contamination in the year 2000, decreasing to  $5 \times 10^{9}$

cm<sup>-2</sup> of iron in 2005 [1]. These low levels of acceptable contamination require ultra pure environment on all steps of the technological process for the dedicated devices.

Iron is certainly one of the most troubling contaminants in the IC industry. Iron is a very common element in nature, and is difficult to completely eliminate on a production line. Therefore, the unintentional iron contamination level in wafer is higher than that of other metal impurities [4].

Iron related defects have been studied in iron-doped samples at different temperatures under different reverse voltages.

DLTS technique is the only electrical technique that can measure electrically active defects down one part in billion. It therefore, inspired me to work on DLTS system for getting a comprehensive picture of the system design. The main purpose of the this project was to develop a Digital Computerized Deep Level Transient Spectroscopy (DLTS) system in our Advance Materials Physics Laboratory (AMPLAB) thereby attaining a comprehensive understanding of hardwaring, softwaring and its different operational features. The shipment of the parts was not done in time. In spite of this, system is developed with little resources in limited time. Improvements and extensions to its present capabilities are possible.

#### 1.4 Scheme of Thesis

Chapter 2 included the historical background on the different defect states associated with different transition metals (TM) e.g Ag, Au and Fe, their complexes with intrinsic defects. It provides the information about different characteristics of these defects, like capture cross-section, activation energy, emission rates, and defect concentration. This chapter also included the history of quenched-in defects, especially those associated with iron. The complexes of iron with boron or other impurities and its defect states whether stable, unstable or metastable are also studied.

In chapter 3 a brief description of current-voltage and capacitance-voltage characteristics, single-shot technique and Deep Level Transient Spectroscopy (DLTS) is studied. The principle and theory of the DLTS is discussed. Chapter 4 deals with the development of DLTS. Hardware is explained in detail in this chapter. Interfacing of the

devices with PC through GPIB cards is configured. Coupling circuit is designed, assembled, and interfaced for pulses width of nanosecond. To communicate with all these devices for measurements, a software in Visual C++ has been programmed.

The final chapter 5 explains the experimental details including the electrical measurements, single shot and deep level transient spectroscopy measurements. The results are discussed and compared with literature. Possibilities of enhancement of digital computerized DLTS system are discussed.

#### References:

- [1] SIA, International technology roadmap for semiconductors. <u>www.itrs.net/ntrs/publntrs.nsf</u>, <u>www.sematech.org</u>

- [2] Seongbok Lee, John D. Dow and Otto F. Sankey, Phys. Rev. B31, 3910(1985)

- [3] M. Zafer Iqbal Proceedings of 6<sup>th</sup> International Workshop on Physics of Materials, Jamia Millia Islamia, New Delhi India, 1987, ed. By Z.H. Zaidi and M. Hussian, p.24 (1989)

- [4] L.Jastzebski, J.Lagowski, W.Henley, P.Edelman: In Beam-Solid Interaction for Material synthesis and Characterization, edited By D.C Jacobson, D.E Luzzi, T.F.Heinz, M. Iwaki (Mater. Res. Soc., Pittsburgh 1995) p. 576

# 2

## Historical Review of Iron-related Defects in Silicon

#### 2.1 Introduction

Invention of transistor has made tremendous progress in silicon technology. Device performance has been improved by at least a factor of a million in every respect. The number of transistors per chip has increased to 200 million for 256 MB DRAM and 20 million for microprocessor. This became only possible because the growth of device is controlled in sense of defects and impurities related to iron and other elements contamination. The Semiconductor Industry Association (SIA) International Technology Roadmap specified  $1.4 \times 10^{10}$  cm<sup>-2</sup> as the maximum allowable surface iron contamination in the year 2000 and targeted to decrease to  $5 \times 10^9$  cm<sup>-2</sup> of iron in 2005 [1]. Iron is certainly one of the most troubling contaminants in IC industry. Iron is fast diffuser in silicon as compare to other transition metals (TM). Iron is very common element in nature, and is difficult to completely eliminate on production line. Therefore, the unintentional iron contamination level in wafer is usually higher than that of other metal impurities [2]. So iron contamination is detrimental to performance of silicon devices.

Research has been carried out on the fundamental physical properties of iron, impact of iron on device performance, possible sources of iron contamination in production line, and the reaction paths of iron in silicon wafer during growth of device. A review is written about iron-related isolated and complex defects, concentration of iron on surface  $\int \xi$

ich

#### 2.2 Brief History:

and in bulk of silicon.

In 1957, C.B. Collins and R.O. Carlson studied the iron contamination in silicon. They observed that iron introduced a donor level at 0.40 eV from the valance band in melts and diffused doped p-type silicon at 1200  $^{\circ}$ C. This level converts anomalously to a level at 0.55 eV from conduction band at room temperature. This conversion occurs in the order of a month at room temperature and speeds up to about 5 hours at 50  $^{\circ}$ C. The conversion is reversible in range from 70  $^{\circ}$ C ~200  $^{\circ}$ C. Above 200  $^{\circ}$ C, the iron has precipitated in the volume or at the sample surfaces [3]. No accepter level is observed. The electrically active solubility of iron, 1.5x10<sup>16</sup> cm<sup>-3</sup> at 1200  $^{\circ}$ C, is higher than the radiotracer solubility because sample was rapidly quenched in water.

Woodbury and Ludwig (1960) [4], measured the solubility of iron in silicon. Maximum solubility of iron in silicon was  $1.5 \times 10^{16}$  cm<sup>-3</sup>. Donor level was at E<sub>V</sub>+0.40eV. They observed the unchanged resistivity on the diffusion of iron in n-type silicon

In 1964, Bemski and Dias quenched p-type silicon from 600  $^{\circ}$ C ~800  $^{\circ}$ C to room temperature. They measured that bulk resistivity increased with increasing temperature. They also measured that donor concentration had increased with increasing temperature. They observed a stable donor level at E<sub>v</sub>+0.40 eV [5].

In 1967, Elstner and Kamprath obtained same results as Bemski using same resistivity measurements technique [6].

In 1974, Yau and Sah measured two levels at  $E_c$ -0.264 eV and  $E_c$ -0.54 eV in gap of silicon [7]. Iron diffused silicon p-n junctions were heat treated at elevated temperature for long time and quenched to room temperature. They measured that Phosphorous gettering could not remove these defects but slow quenching did so. They suggested that these deep levels were associated with the same iron center.

In 1977, J.D. Gerson, L.J. Cheng, and J.W. Corbett, reported that fast cooling or quenching creates defects in silicon crystals. They pointed out that silicon crystals contains many impurities as found by chemical and physical analysis [8]. Most of these defects are electrically inactive or in precipitates in crystal at room temperature. But at elevated temperatures, these precipitates become active and dispersed into crystals. Quenching to room temperature prevents from the precipitation. It was observed by Lee et al [9] by using an EPR spectroscopy for quenched silicon that iron (Fe<sup>0</sup>) exits in silicon at interstitial sides. He observed that iron was present in as grown silicon and moved to the T<sub>d</sub> interstitial site on heat treatment. They studied majority carrier trapping level in p-type silicon by deep level transient spectroscopy (DLTS) [10]. They used boron–doped polished wafers of float zone (FZ) crystals of 1-, 4-, 10-, and 100- $\Omega$ cm resistivities and Czochralski (CZ) crystals of 2- and 10- $\Omega$  cm resistivities. They were heated from 900-1200 <sup>o</sup>C in atmosphere of nitrogen for 1h and then cooled to room temperature at a cooling rate of ~10<sup>3</sup> <sup>o</sup>C/min. DLTS measurements were taken and two defects located at E<sub>v</sub>+0.45 and E<sub>v</sub>+0.48 eV were found with majority-carrier capture cross-sections 4x10<sup>-18</sup> and 2x10<sup>-16</sup> cm<sup>2</sup> respectively. They found the activation energy for the formation of the E<sub>v</sub>+0.45 eV level to be 2.8±0.04 eV which is comparable with the value obtained by Lee et al [11] and Swanson [12].

In 1983, L.C. Kimerling and J.L. Benton studied the interstitial iron substitutional boron pair (Fe<sub>i</sub>-B<sub>s</sub>) and, association and dissociation reactions in silicon by capacitance transient techniques. The samples were consisted of p-type, <100>, (FZ) and boron doped  $(10^{13}-10^{16} \text{ cm}^{-3})$  silicon. Iron was introduced into silicon by scraping a wire on both surfaces and then rapid thermal annealing at 1200 <sup>o</sup>C for 5 second in flowing argon ambient. Schottky diodes were constructed by evaporating Ti at room temperature. In p-type material the boron related acceptor level at E<sub>v</sub>+0.45 eV and interstitial iron donor level at E<sub>v</sub>+0.39 eV were observed. The latter was observed by applying reverse bias. It is found that the pair is a simple association of two point charges; the defects are perturbed by minority carrier injection in such away that the boron acceptor level moves toward valence band and the interstitial iron donor level toward conduction band. Above 77 k the dissociation process retarded [13].

In 1983, S.D. Brotherton, P. Bradley, A. Gill and B.R. Weber used Electron Para Magnetic Resonance (EPR), diode capacitance measurements and deep level transient spectroscopy (DLTS) to identify the levels in silicon associated with the Au-Fe complex. They found two levels at  $E_c$ -0.354 eV and  $E_v$ +0.434 eV. Low-temperature annealing confirmed them as the gold-related complex. They used two sets of samples. A-type samples were for EPR and DLTS and B-type for electrical measurements. A-type was (FZ) n-silicon doped with  $7x10^{15}$  Phosphorus atom /cm<sup>3</sup>. Gold was diffused for 1 to 10h at  $1100~^{0}$ C and rapid quenched to room temperature. EPR revealed the presence of the Au-Fe complex indicating iron contamination during diffusion [14]. The type B samples were p<sup>+</sup>n and n<sup>+</sup>p diodes. The n-type diode was fabricated on  $102-\Omega$ -cm (FZ). This sample was implanted with  $10^{14}$  iron ions /cm<sup>2</sup> at 180keV for 30 min at  $1000~^{0}$ C and then rapidly quenched to room temperature. The n<sup>+</sup>p diode was fabricated on  $66-125~\Omega$ -cm (FZ). A thin film of iron was evaporated onto the back face for 30 min at  $900^{0}$ C followed by rapid quench to room temperature.

Indusekhar and V. Kumar (1986) [15], used TSCAN and DLTS and observed two levels at  $E_v$ +0.42 eV and  $E_c$ -0.52 eV in p-type silicon. They observed that these defects were thermally induced. The source of contamination was quartz tubes and heater filaments at elevated temperature. They noted that  $E_v$ +0.42 eV was a complex centre.

In 1987, N. Balasubramanyam and V. Kumar observed that thermal processes such as fast cooling or quenching from elevated temperature can create defects in p-type silicon. These defects are due to iron introduced during various steps of device processing. A hole trap is observed at  $E_v$ +0.4 eV in quenched p-type silicon. They observed two levels at  $E_c$ -0.54 and  $E_c$ -0.29 eV in quenched n-type silicon. The capture cross section of such deep level is  $(1.0x10^{-15} \text{ cm}^2)$  lager than shallow level of order  $10^{-16} \text{ cm}^2$  and has a T<sup>-2</sup> dependence. The samples were epitaxial silicon of thickness  $10\mu$ m formed on highly doped n-typed silicon. Layer of oxide is grown on the n-Si layer by dry oxidation at 1160  $^{0}$ C in a quartz tube for 90 min. DLTS was used to take measurements [16].

Hiroshi Nakashima, Takashi Isobe, Yuhide Yamamoto and Kimio Hashimoto in 1988, observed the diffusion coefficient ( $D_{Fe}=3.3 \times 10^{-1} \exp(-0.81/\text{KT}) \text{cm}^2/\text{s}$ ) of iron in silicon wafer. These wafers were p-type F.Z (111) with a boron concentration of  $1.2 \times 10^{15}$  cm<sup>-3</sup> at room temperature in the range between 0 and 70 °C. The iron deposited wafer was heat-treated between 950 °C and 1057 °C in vacuum for 1.5 to 2.5h and then quenched into liquid nitrogen. DLTS spectra of sample diffused with iron for 4h showed two pcaks at around 70 K and 240 K. The thermal emission activation energies of the hole traps were 0.10±0.01 eV and 0.45±0.02 eV from the T<sup>2</sup> correction of the emission rates [17].

In 1989, Kakishta et al, observed three deep levels at  $E_c$ -0.21,  $E_c$ -0.36 and  $E_c$ -0.08 eV in iron-doped silicon by DLTS. They observed that these defects are mobile during storage at room temperature. The origin of these levels is iron-related complexes in silicon [18].

In 1992, H. Nakashima et al, studied metastable iron-boron pairs in p-type silicon by using DTLS, TSCAN, and single shot techniques with minority–carrier injection. Two levels at  $E_v$ +0.53 and  $E_v$ +0.48 eV are observed as the metastable pairs after the injection at 150 K. The level at  $E_v$ +0.53 eV consisted of two traps which vanish with different decay rates at around 220 K but the level at  $E_v$ +0.48 eV annihilates with simple exponent ional form [19].

In 1993, H. Nakashima et al [20], measured metastable  $Fe_i$ -B<sub>s</sub> pair in silicon using dark or photo capacitance transient technique combined with minority carrier injection below 200 K. Five levels at E<sub>c</sub>-0.43, 0.46, 0.52, 0.54 and E<sub>v</sub>+0.53 eV were observed. They noted that levels at E<sub>c</sub>-0.43 eV, E<sub>v</sub>+0.53 eV and E<sub>c</sub>-0.54 eV were originated from  $Fe_i^{+/-}$  that appeared at 2<sup>nd</sup>, 3<sup>rd</sup>, and 4<sup>th</sup> nearest T<sub>d</sub> sites adjacent to B<sub>s</sub><sup>-</sup> respectively.

In 1995, Shuji Tanaka and Hajime Kitagawa observed that iron introduced a donor level at  $E_c$ -0.4 eV with several acceptor levels [21]. It means that positively and negatively charged iron states coexist in n-type silicon. They used phosphorus-doped n-

type, FZ and dislocation-free silicon crystals. The temperature and time of the diffusion ranged from 1130 <sup>o</sup>C to 1190 <sup>o</sup>C and 30 min to1h respectively followed by rapid quenching into liquid nitrogen. They used DLTS and steady state capacitance technique for this sample. They observed that donor concentration decays during storage at room temperature.

In 1997, T. Sadoh et al, noted two deep levels in n-type silicon using thermally stimulated capacitance technique (TSCAP) combined with minority carrier injection. These levels were at  $E_v$ +0.31 and  $E_v$ +0.41 eV. The level at  $E_v$ +0.41 eV is due to interstitial iron and first one is due to complex of interstitial and hydrogen. The sample was annealed at 175  $^{0}$ C for 30 min. They noted that transition metals such as vanadium [22], chromium [23], and iron tend to form complexes with hydrogen in n-type silicon. These complexes induce donor levels below the donor levels of the isolated interstitial species.

In 1998, Shuji Tanaka et al observed that the diffusion and electrical characteristics of iron in n-type silicon are less established than those in p-types silicon [24]. They used DLTS and Hall Effect measurement techniques and observed that only a small fraction of iron atoms dissolved can be ionized. They also observed that iron-related defects in CZ-grown n-type silicon were identical to those in floating zone (FZ)-grown n-type silicon. Samples were phosphorus-doped dislocation-free, FZ- and CZ-n-type silicon. The phosphorus concentration in these samples was found  $4\times10^{13}$  to  $4\times10^{14}$  cm<sup>-3</sup>. The samples were divided into smaller slices. Iron was deposited on both the surfaces of the slice by vacuum evaporation.

In 2004, Daniel Macdonald et al, used Deep Level Transient Spectroscopy (DLTS) technique and observed that the interstitial iron (Fe<sub>i</sub>) produced deep level in the band gap which had larger capture cross section than holes [25]. According to the Shockley-Read-Hall (SRH) model, the low-injection carrier lifetime should be much lower in p-type silicon (p-Si) than in n-type (n-Si). The recombination strength of a given impurity is determined by three parameters: the energy level and the capture cross sections for both electrons and holes. The iron-doped sample were prepared by ion implantation with dose of  $10^{11}$  cm<sup>-2</sup> and annealed at 900 <sup>o</sup> C for 1h. The float-zone (FZ)

n-si samples of resistivity 2- $\Omega$  cm (N<sub>D</sub> =2.4x10<sup>15</sup> cm<sup>-3</sup>) and 260  $\mu$ m thickness and p-si (FZ) wafer of 5- $\Omega$  cm (N<sub>A</sub>=2.8x10<sup>15</sup> cm<sup>-3</sup>) and 290  $\mu$ m thickness were used.

In 2004, L.J. Geerligs and Daniel Macdonald investigated the dynamics of lightinduced dissociation of iron-boron (FeB) pairs in p-type silicon. They observed that dissociation was single-exponential process which was balanced with thermal repairing. The dissociation rate is proportional to the square of the carrier generation rate and the inverse square of the FeB concentration. This shows that the dissociation process involves the two recombination or electron capture events. The float-zone (FZ) samples were contaminated with Fe by implantation or diffusion. They used quasi-steady-state photo conductance (QSSPC) to measure the carrier life time [26].

The review reveals that a lot of research has been done on iron contamination, defect levels, and iron concentration under different parameters in silicon. In spite of this research, some ambiguities and controversies still exist. So some aspects need further investigations especially the formation of stable defects in one kind of samples and unstable in other kind of samples.

#### References:

- [1] SIA, International technology roadmap for semiconductors. <u>www.itrs.net/ntrs/publntrs.nsf</u>, <u>www.sematech.org</u>

- [2] L.Jastzebski, J.Lagowski, W.Henley, P.Edelman: In Beam-Solid Interaction for Material synthesis and Characterization, ed. By D.C Jacobson, D.E Luzzi, T.F.Heinz, M. Iwaki (Mater. Res. Soc., Pittsburgh 1995) p. 576

- [3] C.J. Gallagher [Phys. Rev. 100, 1259(A) (1955)]

- [4] H.H Woodbury and G.W. Ludwing, phys. Rev.1, 102 (1960)

- [5] G.Bemski and C.A. Dias, J. Appl. Phys. 35, 2985(1964)

- [6] L. Elsner and W. Kam prath, Phys. Stat. Sol.22,541(1967)

- [7] L.D. Yau and C.T. Sah, Solid State Electron. 17,193(1974)

- [8] A. Mayer, Solid state Technol. 15, 1138 (1972)

- [9] Y.H. Lee, R.L. Kleinhenz, and J.W. Corbett, Appl. Phy. Lett. 31, 142 (1977)

- [10] D.V. Lang, J. Appl. Phys. 45,7 (1974)

- [11] Y.H. Lee, R.L. Kleinhenz, and J.W. Corbett, Appl. Phy. Lett. 31, 142 (1977)

- [12] M.L. Swanson, Phys. Status Solidi 33, 721 (1969)

- [13] L.C. Kimerling and J. L. Benton Physica, B116, 297(1983)

- [14] Y.H Lee, R.L. Kleeinhenz, and J.W.Corbett, Inst. Phys. Conf.Ser.46, 521(1979)

- [15] H. Indusekhar and V. kumar, Phys. Stat. A95, 269(1986)

- [16] R.N. Srinath, M.M. Chandra, and G Suryas Proe. Inst.electr.Engr., part I 131,63 (1984)

- [17] E. Weber: Appl. Phys. A 30 (1983)

- [18] H. Nakashima, T Sadoh and T. Tsurushima 17<sup>th</sup> (ICDS-17)

Gmunder (1993)

- [19] K. Graff and H. Pieper, J Electrochem. Soc. 128, 669 (1981)

- [20] H. Nakashima, T Sadoh and T. Tsurushima 17<sup>th</sup> (ICDS-17) Gmunder (1993)

- [21] H. Kitagawa, L.c. kimerling and S. Tanaka: J. Electron Mater. 21 (1992) 863

- [22] H. Nakashima, T Sadoh and T. Tsurushima J. Appl. Phys. 72,520 (1992)

- [23] H. Nakashima, T Sadoh and T. Tsurushima J. Appl. Phys. 75, 3978 (1994)

- [24] C. Schmidt: Appl. Phys. 17 (1978) 137

- [25] A.A. Iatratov, H. Hieslmair, and E.R. Weber, Appl. A: Mater.Sci. Process. 69, 13 (1999)

- [26] G. Zoth and w. Berghholz, J. Appl. Phys. 67, 6764(1990)

# 3

## Physics of P<sup>+</sup>n Junction & Electrical Techniques

This chapter explains the theoretical aspects of p-n junction and it characteristics. Current-voltage characteristics, capacitance-voltage characteristics, single shot transient technique, and deep level transient spectroscopy (DLTS) are explained in detailed.

#### 3.1 Current-Voltage (I-V) Characteristics

The most important property of p-n junction diode is its ability to offer very little resistance to the current flow in the forward bias direction and maximum resistance to the current when reverse biased. Transition region or depletion region of the p-n junction changes with varying applied voltage. When diode is reversed bias the depletion region increases. The only charge carriers able to support a net current across the p-n junction are the minority carriers and hence the reverse current is very small. A forward-biased diode has a decreased depletion region; the majority carriers can diffuse across the junction. The voltage may become high enough to eliminate the entire depletion region. An approximation to the current I of a p-n junction is usually written as a function of the diode voltage  $V_d$  as

$$I = I_{\theta} \left( \exp \left( \frac{q V_d}{n k T} \right) - 1 \right)$$

3.1

Where  $I_{\theta}$  is the saturation current and *n* is the diode ideality factor. The ideality factor *n* incorporates all those unknown effects making the device nonlinear. The diode voltage  $V_d$  is the voltage across the space-charge region and excludes any voltage drops across the p and n quasi-neutral regions. *K* is Boltzmann's constant. T is the temperature of the diode. Here  $I_{\theta}$  is temperature dependent. This equation gives a reasonably accurate prediction of the current-voltage relationship of the p-n junction itself, especially due to the temperature variation. The saturation current is given as

$$I_{\theta} = AA^* T^2 \exp\left(\frac{-q\phi_B}{kT}\right)$$

3.2

Where, A is the area of the diode.  $A^*$  is the Richardson constant [1] corrected by the effective mass:

$$\mathbf{A}^* = \mathbf{A} \left( \frac{m_n^*}{m_e} \right) \tag{3.3}$$

Where  $m_n^*$  is the effective mass of the electrons and  $m_e$  the mass of the single electron. If the diode voltage  $V_d >> nKT$ , equation 3.1 becomes as follow:

$$I = I_0 \exp\left(\frac{qV_d}{n kT}\right)$$

3.4

The equation 3.4 can be written in linear form by taking the log on both sides of this equation. The linear form of the equation 3.4 is given as:

$$\ln (I) = \ln (I_0) + \left(\frac{qV_d}{nkT}\right)$$

3.5

This is equation of straight line [2]. We can calculate ideality factor *n* from the slope of this line. The value of ideality factor *n* determines which type of current dominates. If the value is n = -1, then diffusion current dominates. If the value of *n* is -2, then recombination current dominates. If 1 < n < 2 then both currents are present. Where,  $\ln (I_0)$  is the intercept of this line. We can also calculate potential barrier height  $\phi_B$  [3] using equation 3.2

$$q\phi_B = kT \ln\left(\frac{AA^*T^2}{I_0}\right)$$

3.6

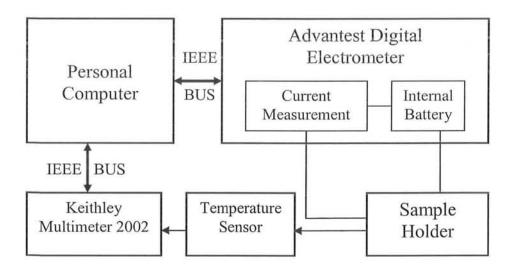

Block diagram for current-voltage is shown in figure 3.1

#### 3.2 Capacitance – Voltage (C-V) Characteristics

The p-n junction is an interface between two substrates having different doping profiles of silicon. The metallurgical p-n junction is formed by the diffusion of carriers because of their concentration gradient. This metallurgical junction develops two layers of opposite charges at its edges. So this metallurgical junction acts as a capacitor. There are basically two kinds of capacitance associated with this junction. The junction capacitance is due to the dipole of charges in the transition region. It is also called depletion layer or transition region capacitance. As diffusion current increases, voltage lags behind that produces the change in capacitance. This capacitance is called charge storage capacitance. It is often called the diffusion capacitance. The junction capacitance is dominant under reverse bias and the charge storage capacitance is dominant under forward bias.

Capacitance is defined as the differential flow of the charge into plate with respect to the change in applied voltage as follow:

$$C = \left| \frac{dQ}{dV} \right|$$

3.7

Where Q is charge on each side of the transition region and V is the applied voltage. Since the charge Q on each side of the transition region varies nonlinearly with applied voltage, the width of transition depends on value of applied voltage. Since we are dealing with nonequilibrium case with applied voltage so electrostatic potential barrier changes to  $(V_0-V)$ . Width of the transition region is given as follow:

$$W = \left[\frac{2\varepsilon \left(V_0 - V\right)}{q} \left(\frac{N_a + N_d}{N_a N_d}\right)\right]^{1/2}$$

3.8

Where,  $N_a$  and  $N_d$  are the concentrations of the acceptor and donor impurities.

It is clear from expression 3.8 that applied voltage V can be either positive or negative for forward or reverse bias. The width of the transition region increases with the decrease in reverse bias and it decreases with increase in forward bias. Since the uncompensated charge Q on each side of the junction varies with the transition region, the value of Q can be written in terms of the doping concentration and transition region width on each side of the junction as follow:

$$\left|\mathbf{Q}\right| = \mathbf{A} \left[ 2q\varepsilon \left( \mathbf{V}_0 - \mathbf{V} \right) \left( \frac{N_a N_d}{N_a + N_d} \right) \right]^{1/2}$$

$$3.9$$

Where A is the area of the sample and  $\varepsilon$  is permittivity of silicon.

The expression 3.9 shows that the charge Q is nonlinear function of applied voltage. The junction capacitance  $C_j$  is calculated from equation 3.7 and after taking derivative of equation 3.8 with respect to potential barrier difference.

$$C_{j} = \varepsilon A \left[ \frac{q}{2 \varepsilon (V_{0} - V)} \left( \frac{N_{a} N_{d}}{N_{a} + N_{d}} \right) \right]^{1/2}$$

3.10

$$C_j = \frac{\varepsilon A}{W}$$

3.11

If the junction is asymmetrically doped then the transition region lies primarily into the less heavily doped side, and the capacitance is determined by only one of the doping concentrations. For a  $p^+$  n junction the capacitance is given as follow:

$$C_{j} = A \left[ \frac{\varepsilon q N_{d}}{2 (V_{0}-V)} \right]^{1/2} For p^{+}n \qquad 3.12$$

It is possible to measure the concentration of the lightly doped region using equation 3.12

Linearly graded junction diode is that in which the concentration of the ions varies gradually [4]. The space charge density q  $N_d$  of linearly graded junction varies as:

$$V_{j} = \frac{q N_{d}}{12\epsilon} W^{3}$$

3.13

Junction capacitance of the linearly graded junction can be calculated as

$$C_{j} = A \left[ \underbrace{\frac{\epsilon^{2} q \ \alpha}{12 \ V_{j}}}_{3.14} \right]^{1/3}$$

Where  $\alpha$  is the concentration gradient.

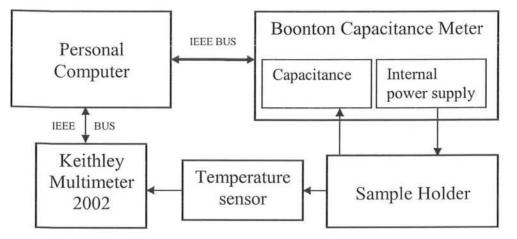

Fig. 3.2 Block diagram for C-V measurements

#### 3.3 Single-Shot Transient Technique.

The equilibrium or steady state of a system can be perturbed by changing the concentration of the carriers. Concentration of carrier can be changed by applied voltage, temperature of the system and light shining. The system is then allowed to relax back. Its relaxation exposes properties of the physical system. Since the temperature has, in many cases, a most pronounced effect on the physical property of the system. So it has to be carefully controlled during the experiment. There are two basic types of relaxation techniques as given below:

- Isothermal relaxation: the system is perturbed at constant temperature and then it

is allowed to relax back and change in capacitance is recorded for a long. The

transient obtained by such measurements gives the time constant/ constants of the

transient and ultimately emission rates are calculated from time constant. This

method of recording transient is known as *single shot measurement*.

- Nonisothermal relaxation: the system is perturbed at a sufficiently low temperature to reduce the probability to establish a new equilibrium. Subsequently, the temperature is increased with help of well-controlled heating program. Thus increasing the reaction rates and the relaxation of the system can be monitored as a function of temperature and time [5].

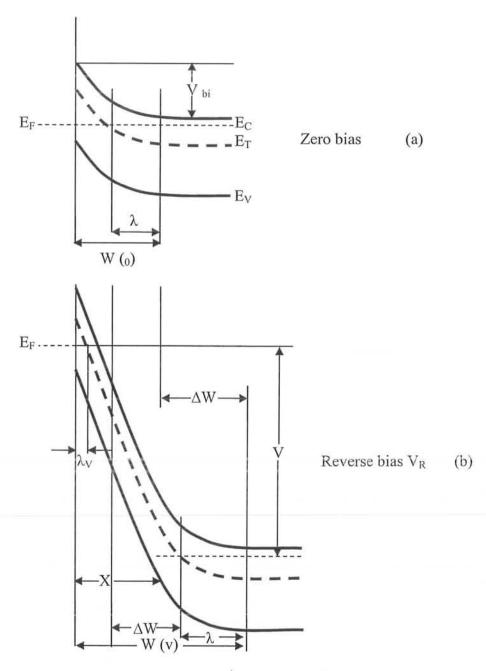

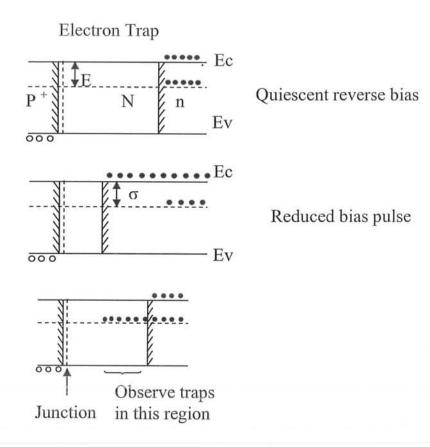

Consider a p<sup>+</sup>n junction in equilibrium at a fixed temperature. The charge carrier population in space charge region of p<sup>+</sup>n junction can be changed by switching the applied bias from zero to a reverse applied voltage. The deep level are filled for  $X > W - \lambda$  and empty for  $X < W - \lambda$  as shown in figure 3.3(a) [6]. This perturbation in space charge region will come to an end to attain steady state equilibrium in a finite time. When the deep levels begin to empty, the transient in form of current or capacitance is recorded. The emission rate of the deep levels can be calculated from the time constant of this transient. We can estimate the density of deep levels filled with the carriers in initial state from the magnitude of this transient. Theory of single shot technique is explained as below:

Fig. 3.3 Band bending diagram for  $p^+n$  junction [7]

According to Shockley-Read-Hall statistics, the recombination kinetics of the charge carriers introduced into space charge region by perturbation process is governed by the following equation.

$$dn_{\rm T}/dt = (nc_{\rm n} + e_{\rm p})N_{\rm T} - (nc_{\rm n} + pc_{\rm p} + e_{\rm p} + e_{\rm n})n_{\rm T}$$

3.15

In space charge region, electrons 'n'

In space charge region, electrons 'n' and holes 'p' are negligibly small and can be neglected[8,9]. The equation 3.15 can be written as:

$$dn_{\rm T}/dt = (e_{\rm p})N_{\rm T} - (e_{\rm p} + e_{\rm n})n_{\rm T}$$

3.16

The equation 3.16 is first order inhomogeneous. The solutions of this equation under condition  $N_T = n_T$  at t=0 are as:

$$n_T = N_T \qquad \qquad \text{for } t \le 0 \qquad \qquad 3.17$$

$$n_{T} = (e_{p})N_{T}/(e_{p}+e_{n})\{1+(e_{n}/e_{p})\exp(-(e_{p}+e_{n})t\} \text{ for } t > 0 \qquad 3.18$$

If  $N_d$  is positive space charge concentration in the space charge region of the width W, then the voltage change induced by trapped electrons n(x,t) at x in the interval  $\Delta x$  at 0 < x < W is given as

$$\Delta V = e/\epsilon \left[ N_d W(\Delta W) - n(x,t) x(\Delta x) \right]$$

3.19

The trap concentration in a space charge region is based on the change in capacitance by the release of the carriers from the trap at constant reverse bias. It is obtained from equation 3.19 by putting  $\Delta V = 0$ ,  $C = \varepsilon A/W$  and  $\Delta C = \varepsilon A/\Delta W$ .

$$\Delta C/C = [n(x,t)/N_d W^2] x \Delta x \qquad 3.20$$

If n(x,t) is only time depended, the electron trapped n(t) are equal to filled traps  $n_T$  and  $n_T = N_T$  which are uniformly distributed, then equation 3.20 can be written as:

$$\Delta C/C = \int [(e_p)N_T/N_d W^2(e_p+e_n)][1+(e_n/e_p)exp\{-(e_p+e_n)t\}]x(dx)$$

3.21

After integrating the equation 3.21 while using  $W = W_v$  at applied voltage  $V_R$  and  $W_0$  at built-in voltage  $V_{bi}$  such that  $W_v >> W_0$ , we get the following equation:

$$\Delta C/C = [(e_p)N_T/2N_d W_v^2(e_p+e_n)][1+(e_n/e_p)exp\{-(e_p+e_n)t\}] W_v^2 \qquad 3.22$$

When electrons are majority carriers i.e  $e_n \gg e_p$  then equation (h) reduces to

$$\Delta C/C = [N_T/2N_d \exp\{-(e_n)t\}]$$

3.23

$$\Delta C/C = [N_T/2N_d \exp\{-t/\tau\}]$$

3.24

Where  $\tau = 1/e_n$  is the capacitance transient time constant.

$$\Delta C = C N_T / 2N_d \exp\{-t/\tau\}$$

3.25

Taking natural log on both sides we get

$$\ln \Delta C = -t (1/\tau) + \ln (CN_T/2 N_d)$$

3.26

This is an equation of a straight line. The slope of the equation gives the emission rate of electrons. For holes the same procedure is used with convenient changes in parameters.

#### 3.4 Deep Level Transient Spectroscopy

'Deep Level Transient Spectroscopy (DLTS) was developed in 1974 by D.V. Lang [10] to investigate energetically "deep" charge trapping levels in semiconductor space charge structures, which may be either pn junctions or Schottky barriers. It utilizes the fact that the reference capacitance of the sample depends on the charge state of deep levels in the space charge region. In total depletion approximation, the reference capacitance of a sample having a homogeneous doping concentration is:

$$C_0 = A_{\sqrt{\frac{\varepsilon \varepsilon_0 e \left(N_D - N_A\right)}{2(V_r + V_d)}}}$$

3.27

Here A is the sample area,  $N_D$ - $N_A$  is the total net charge density in the space charge layer (SCL),  $V_r$  is the reverse bias,  $\varepsilon\varepsilon_0$  is the permittivity of the semiconductor material, and e is the electron charge. If the sample is a pn junction,  $N_D$ - $N_A$  refers to the lower doped side of the junction.  $V_d$  is the built-in diffusion voltage of the space charge structure, which is the crossing point of the extrapolated  $1/C^2$  plot vs  $V_r$  with the  $V_r$ -axis. If A is measured in units of mm<sup>2</sup>,  $N_D$ - $N_A$  in cm<sup>-3</sup>,  $C_0$  in pF, and  $V_r$ + $V_d$  in V, eq. 3.27 leads to the following relation with adapted units:

$$N_{\rm D} - N_{\rm A} \left[ {\rm cm}^{-3} \right] = 1.41 * 10^{12} \frac{C_0 [{\rm pF}]^2 (V_{\rm r} + V_{\rm d})}{A [{\rm mm}^2]^2 \epsilon}$$

3.28

If charged trapping levels are existent in the SCR, their space charge has to be added to  $N_D-N_A$  [11]. Assuming a donor-like trap level of concentration  $N_t$  in an n-type sample biased under a reverse bias  $V_r$ , the capacitance change by recharging these levels is

$$\Delta C = A \sqrt{\frac{\epsilon \epsilon_0 e (N_D - N_A)}{2(V_r + V_d)}} - A \sqrt{\frac{\epsilon \epsilon_0 e (N_D - N_A + N_t)}{2(V_r + V_d)}} \cong C_0 \frac{N_t}{2(N_D - N_A)}$$

3.29

The last identity holds approximatively if  $N_t \ll N_D - N_A$  holds. Then the trap concentration calculates from the capacitance change  $\Delta C$  as:

$$N_{t} = \frac{2\Delta C}{C_{0}} (N_{D} - N_{A})$$

$$3.30$$

Reverse bias

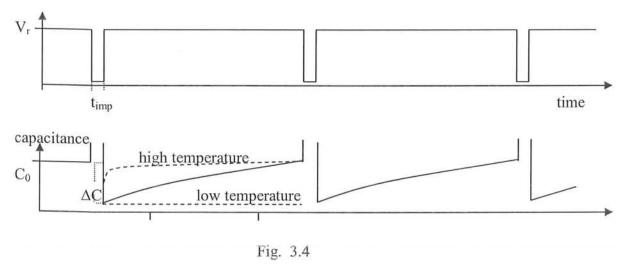

#### 3.5 DLTS Measurement Procedure

The DLTS measurement i.e. the capacitance transient of the sample is measured under the reverse voltage bias  $V_r$  when the bias pulses are periodically applied to the sample. This leads to a periodic recharging of the levels in the SCR (Space Charge Region). Its reverse bias  $V_r$  is reduced or even reversed for a certain filling pulse width  $t_p$ . During these pulses the reference capacitance changes. Immediately after each pulse the reference capacitance changes by  $\Delta C$ , whereby  $\Delta C$  is negative for majority carrier traps and positive for minority carrier traps as shown in figure 3.4. If a Schottky diode is used, or if in a pn junction the reverse bias is only reduced by a pulse bias  $V_p \leq V_r$ , only majority carrier traps are recharged. If during the pulse a pn junction is forward-biased by injection, also minority carriers may be recharged. The degree of trap filling depends on the filling pulse width  $t_p$  and on the capture coefficient of the traps  $c_{n;p}$ , which is often formally expressed as the product of the thermal velocity times the capture cross section of the trap for the corresponding carrier type. For the filling of traps in space charge region (SCR), the pulse width  $t_p$  of the pulse should be large enough with the pulse period  $t_w$ . Hence all deep levels in the SCR will be filled by the pulse. For sufficiently small pulses only some part of all levels are filled, hence the signal gets smaller. The pulse width  $t_p$ , for which the signal height has reduced to 1/e = 0.367 of its maximum value, allows one to measure the capture coefficient  $c_n$  for electrons or  $c_p$  for holes:

$$C_{n;p}=(n;p)/t_p$$

3.31

Here n and p are the free carrier concentrations of electrons and holes, respectively, during the capture process. Equations 3.30 and 3.31 only hold if  $\Delta V$  is large compared to  $V_d$  and close to  $V_r$ . For  $\Delta V < V_r$  the trap concentration calculated for saturation pulses for homogeneous trap distributionis is as follow:

$$N_{t} = \frac{2\Delta C V_{r}}{C_{0} \Delta V} (N_{D} - N_{A})$$

3.32

Hence, for homogeneous trap distribution the DLTS peak height  $\Delta C$  is expected to be proportional to the filling pulse height  $\Delta V$ . Note that the equilibrium degree of trap filling in the SCR under reverse bias is zero, hence the levels are ionized. If after a filling pulse traps are filled and the reverse bias is re-established, the system is in thermal nonequilibrium and relaxes into equilibrium by thermally emitting the trapped charges into the corresponding bands, where they are swept away by the electric field. For isolated point defects this relaxation is exponential in time, but for extended defects like dislocations, precipitates, and interface layers the emission transient i.e. just as the trap filling process, may be non-exponential. Therefore all these relations strictly only hold for point defects. This relaxation is connected with a capacitance transient, which is converted into a measurable transient signal by a capacitance-meter [12]. The time constant  $\tau_e$  of the thermal emission is governed by the thermal emission rate  $e_{n;p}$ , which depends on the trap energy  $E_t$  and on the temperature T:

$$e_{n;p} = \frac{1}{\tau_e} = \frac{N_{c;v} c_{n;p}}{g} exp\left(\frac{-E_t}{kT}\right)$$

3.33

Here  $N_{c;v}$  is the effective density of states in the conduction band for electron emission or the valence band for hole emission, respectively, g is the degeneracy factor of the level, usually assumed to be unity, and kT is the thermal energy. Hence, the thermal emission rate  $e_{n;p}$  is the inverse of the emission time constant  $\tau_e$ . The exponential dependence of the emission rate on 1/T that is called the Arrhenius plot, with the thermal energy  $E_t$ determining its slope and the capture coefficient  $c_{n;p}$  determining its prefactor, is the signature of each trap, which is used for their identification.

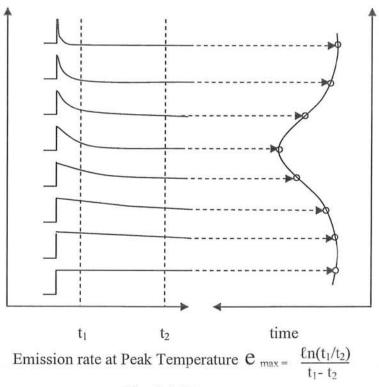

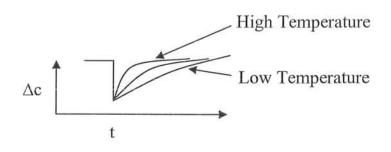

In DLTS filling pulses are applied periodically to the sample, leading to periodical capacitance transients as shown in figure 3.4. The basic idea of DLTS is to convert the capacitance transients into the DLTS-signal by "correlating" them on-line. The simplest kind of DLTS correlation is the 2-point correlation, where the capacitance is measured at two times  $t_1$  and  $t_2$  after the end of each filling pulse, and the difference between these two values is displayed:

Output signal

$$=a[C(t_2)-C(t_1)]$$

3.34

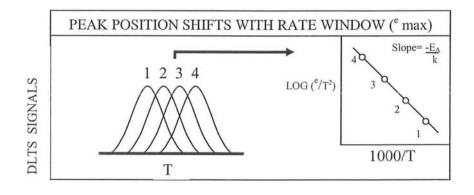

Hence, the DLTS signal is scaled in units of capacitance (usually pF) [13,14]. Other kinds of correlation are providing an especially good signal-to-noise ratio (exponential correlation) or a better energy resolution (high resolution correlation) than 2-point correlation. Usually the DLTS measurement starts at low temperature, the temperature is slowly ramped up, and the DLTS signal is recorded. During the T-ramp the relaxation time constants of all levels in the sample are gradually increasing from very large values to very low ones according to eq. 3.33. As long as T is too low for significant thermal emission until  $t_2$ , the difference is zero (eq 3.34). It is shown in "low temperature" trace in figure 3.4. If T is so high that the relaxation is already over at  $t_1$ , the difference is also zero and it is shown in "high temperature" trace in figure 3.4 Only if the emission time constant or the emission rate, respectively, of one level falls into the so-called "rate window" given by the selection of  $t_1$  and  $t_2$ , a DLTS peak appears [15,16]. For 2-point correlation we obtain the following condition for the DLTS peak to appear:

Fig. 3.5 (b)

Fig. 3.5 (c)

## 3.6 Deep Level Defects Characteristics

Deep level defects present in space charge region are characterized by different parameters. These parameters are tools to know all about the nature of these defects. Detailed knowledge is necessary about these parameters. Without these we are not able to have conformed information about their binding energy, depth profile, and nature of the defects. Following are the parameters of deep level defects which are usually studied using DLTS technique.

- Thermal Emission Rate

- Thermal Activation Energy

- Deep Level Concentration

- Capture Cross-sections

#### 3.7 Thermal Emission Rate

When  $p^+n$  junction is biased by applying sufficiently high reverse bias but smaller than the breakdown voltage followed by repeated pulses from this reverse bias to close-to-zero volt, transient due to emission of the charge carriers recorded by DLTS. The temperature of the sample is continuously changed. Emission and capture processes are present there [19, 20]. The net rate of electron emission is given by

$$dn_T / dt = c_n p_T n - e_n n_T \qquad 3.36$$

When junction is perturbed by reverse bias, the number of filled and unfilled traps will change due to this perturbation. The transition of the effected levels will decay to steady state at time  $t = \infty$  i.e

$$\mathbf{e}_{n} \mathbf{n}_{T}(\infty) = \mathbf{n} \mathbf{c}_{n} \quad \mathbf{p}_{T}(\infty)$$

3.37

In steady state condition, the change in filled and unfilled traps is equal i.e  $n_T = -p_T$ , so the net rate of change of trapped electrons can be written as

Or

$$dn_T / dt = c_n p_T n - e_n n_T = (c_n n + e_n) \Delta p_T$$

$$dn_T / dt = (c_n n + e_n) \Delta n_T$$

3.38

The quantity  $(c_n n + e_n)$  remains constant during the time t, the solution of the equation 3.38 is given as

$$n_T(t) = n_{T(0)} \exp \left[-t (e_n n c_n)\right]$$

3.39

Putting the value of  $c_n$  from equation 3.36 into equation 3.39 we get

$$\Delta n_{\rm T} = n_{\rm T(0)} \exp \left[-t \, e_n \, \{ \, p_{\rm T}(\infty) + n_{\rm T}(\infty) \} / p_{\rm T}(\infty) \right]$$

3.40

The occupancy of the electron by the trap is define as

$$f = n_T / (n_T + p_T)$$

3.41

From equation 3.40 and equation 3.41 we get

$$f(t) - f(\infty) = (f_0 - f_\infty) \exp \{(-te_n)/(1 - f_\infty)\}$$

3.42

If the final state is empty in that case  $f_{\infty} = 0$  then equation 3.42 becomes as

$$f(t) = f(_0) \exp(-e_n t)$$

3.43

Taking natural log on both sides, the equation becomes as

$e_n = -1/t \ln \{ f(t)/f(_0) \}$  3.44 It is clear from equation 3.44 that the emission rate of the electrons is reciprocal to the time constant of the transient.

Emission process is shown in figure 3.6

### 3.8 Thermal Activation Energy.

According to Shockley- Read-Hall theory, the emission rate of the carriers can be related to the capture cross-section as given below,

$e_n = \sigma_n \langle V_n \rangle N_c \exp \{-(E_c - E_T)/(kT)\}$  3.45 Similarly emission rate for hole traps is given below as

$$e_p = \sigma_p \langle V_p \rangle N_v \exp \{ - (E_T - E_V) / (kT) \}$$

3.46

We can proceed from above equations to calculate the activation energy of electrons and holes respectively. But we will consider only the case of electron trap. These parameters depend on the temperature.

The  $V_{n,p}$  has T <sup>1/2</sup> because V <sup>2</sup> = { (3kT)/(m)}

Similarly  $N_{c,v}$  has  $T^{3/2}$  temperature dependence. The equation 3.45 can be written in term of temperature as follow;

$$e_{n} = AT^{1/2} T^{3/2} \sigma \exp \{(\Delta E)/(kT)\}$$

$$e_{n} = AT^{2} \sigma \exp \{(\Delta E)/(kT)\}$$

3.47

Where, A is constant.

$$\Delta E = E_c - E_T$$

for electrons emission 3.48

$$\Delta E = E_v + E_T$$

for hole emission. 3.49

Taking natural log on both sides of the equation 3.47 we get a equation of straight line [21].

$$\log (e_n/T^2) = \log (A\sigma_n) - \Delta E/kT$$

3.50

The slope of this line gives the activation energy of level.

## 3.9 Deep Level Concentration

This is another parameter by which the number of emitted or trapped carriers from the deep level at temperature is calculated. When a p<sup>+</sup>n junction is reversed bias, the electrons are emitted from those levels which were filled before the application of reverse bias. Emission of these electrons from space charge region changes the capacitance of the junction. This process will continue for a finite time until all the levels above the Fermi level become empty. When high reverse voltage but less than breakdown voltage is applied for such a finite long time to the junction the change in capacitance will tend to maximum. The finite time and maximum change in capacitance can be denoted as t ( $\infty$ ) and  $\Delta C_{(\infty)}$  respectively. Maximum change in capacitance can be written as

$$C_{(\infty)} - C_{(0)} = \Delta C_{(\infty)}$$

3.51

Change in capacitance per unit capacitance is derived in single shot technique which is given as follow:

$$\Delta C/C = [N_T/2N_d \exp\{-t/\tau\}] \qquad 3.52$$

Where  $\tau = 1/e_n$  is the capacitance transient time constant. When  $t \to \infty$  then  $e_n = 0$  and  $\Delta C = \Delta C_{max}$  Applying these conditions to equation 3.52

Capacitance Transient

Fig. 3.6

We get as

$$\Delta C_{\text{max}} / C = N_T / (2 N_d)$$

3.53

$$N_{\rm T} = (\Delta C_{\rm max}/C) 2N_{\rm d} \qquad 3.54$$

Where  $N_T$  is the deep level concentration and  $N_d$  is the shallow level concentration.

#### 3.10 Capture Cross-Section

Consider a  $p^+n$  junction which is biased by a filling pulse. This filling pulse will fill the carriers' traps. If filling time of the pulse is increased then number of the carriers trapped will increase. DLTS scan is taken; the peak of the spectrum corresponds to the emission rate of the carriers. The peak height varies with varying pulse width for a fixed rate window in emission spectrum. The rate of change of filling trap concentration  $n_T$ during the zero bias filling pulse is given as

$$dn_{\rm T}/dt = S_{\rm n} \left( N_{\rm T} - n_{\rm T} \right)$$

3.55

The solution of the equation 3.55 is given by

$$n_T = N_T [1 - \exp(-S_n t)]$$

3.56

Where  $S_n = nc_n = \sigma_n n < V$  th n > r

When steady state reverse bias is restored after the capture time  $t_c$  the filled trap concentration after time t in the upper half of the band gap cab be written as

$$n_{\rm T}(t_{\rm c},t) = N_{\rm T} [1 - \exp(-S_{\rm n} t_{\rm c})] \exp(-t/\tau_{\rm n})$$

3.57

Where  $e_n = 1/\tau_n$  and t is the time measured after the restoration of steady reverse bias. Change in capacitance depends on the change in occupancy of the traps. Change in capacitance of the junction after t<sub>c</sub> can be related to maximum change in capacitance after infinite capturing time is given as

$$\Delta C (t_c) = \Delta C (\infty) [1 - \exp(-S_n t_c)]$$

[1- \Delta C (t\_c)/\Delta C (\oximega)] = \exp(-S\_n t\_c) 3.58

Taking natural log on both sides of the equation 3.58 gives the equation of straight line. The slope of this line gives the capture rate  $S_n$ .

The capture cross-section can be calculated by putting respective capture rates in following equations

$$S_n = \sigma_n \text{ } n < V_{thn} > \qquad For electrons \qquad 3.59$$

$$S_p = \sigma_p p < V_{thp} > \qquad For holes \qquad 3.60$$

Where  $V_{th}$  is thermal velocity of the carriers.

#### References:

- [1] S.M. Sze, Physics of Semiconductor Devices, 2<sup>nd</sup> ed, Wiley, New York 1981, pp 256-263

- [2] C.D. Lein, F.C.T.So and M.A. Nicolet, "An improved forward I-V Method for Non-Ideal Schottky Diodes with high Resistance," IEEE Trans.Electron Dev.Ed, 1502-1503, Oct. 1984.

- [3] K Sato and Y. Yasumura, "Study of the Forward I-V plot for Schottky Diodes Parameter with High Series Resistance," J.Appl. Phys.58, 3655-3657, Nov. 1985

- [4] Beng Streetman ,4<sup>th</sup> Edited 1995 by prentice Hall pp 173-174

- [5] P.Kelly. M.J.Laubitz, P.Braunlich: Phys.Rev.B4.1960 (1971)

- [6] C.G.B. Garrett. W.H. Brattain: Phys.Rev.99.376-387 (1955)

- [7] D. V. Lang, J. Appl. Phys. 45, 3023 (1974) and D.V. Lang, Topics in Applied Physics Vol.37, edited by P.Braunlish, pp.93

- [8] R.N.Hall, "Electron-Hole Recombination in Germanium," Phys.Rev. 87,387, July 1952

- [9] W.Shockley and W.T. Read, "Statstics of the Recombination of Holes and Electrons," Phys.Rev. 87, 835-842, Sept.1952

- [10] D. V. Lang, J. Appl. Phys. 45, 3023 (1974) and D.V. Lang, Topics in Applied Physics Vol.37, edited by P.Braunlish, pp.93

- [11] W.Shockley and "Electrons, Holes, and Traps, "Proc.IRE 46, 973-990, June 1958

- [12] A.F. Tasch, Jr.and C.T Sah, "Recombination-Generation and Optical Properties of

Gold Acceptor in Silicon, "Phys. Rev. B1, 800-809, Jan, 1970

- [13] H.Lefevre and M. Schulz, "Doule Correlation Technique (DDLTS) for the analysis of Deep Level Profiles in Semiconductors," Appl. Phys. 12,45-53, Jan. 1977.

- [14] H.Lefevre and M. Schulz Appl. Phys. 7,45-53, Jan. 1977

- [15] D. V. Lang, J. Appl. Phys. 45, 3022 (1974)

- [16] F.Hasegawa, J.Appl. Phys. 24,1356-1358, Oct. 1985

- [17] G. L. Miller, D.V.Lang, and L.C. Kimerling, "Capacitance Transient Spectroscopy," in Annual Review Material Science (R.A Huggins, R.H. Blue and R.W. Roberts, eds) Annual Review, Palo Alto, CA 7, 377-448, 1977

- [18] D. V. Lang, "Space-Charge Spectroscopy in Semiconductor," in topic in Applied Physics, 37, thermally Stimulated Relaxation in Solids Springer, Berlin, 1979, 93-133

- [19] R.N.Hall, "Electron-Hole Recombination in Germanium," Phys.Rev. 87,387, July 1952

- [20] W.Shockley and W.T. Read, "Statistics of the Recombination of Holes and Electrons," Phys.Rev. 87, 835-842, Sept.1952

- [21] H. Lefevre and M. Schulz Appl. Phys. 7,45-53, Jan. 1977

## CHAPTER

# 4

## Development of Digital Computerized DLTS System

## 4.1 Introduction

A computerized system for deep level characterization in semiconductor has been setup in our laboratory, with the possibility of enhancing both hardware and software. It is based on the well known Deep Level Transient Spectroscopy (DLTS) technique [1]. This system has been setup at much lower cost than commercial systems. A digital approach to the signal processing in deep-level transient spectroscopy (DLTS) systems is introduced. An improved digital averaging scheme for DLTS signal recovery from noise and transient data storage is proposed. Digital averaging techniques can improve the DLTS digital signal processing. Digital averaging techniques are pseudo-logarithmic time averaging and continuous time averaging. Continuous time averaging is well suited for improving overall signal-to-noise ratio (SNR). It is suitable for continuous display and processing of data, and it is more efficient in using the computer resources. This digital computerized DLTS system is based on continuous time averaging technique. The theory of continuous time averaging technique is explained as:

## 4.2 Theory of Continuous Time Averaging Technique

The pseudo-logarithmic averaging is a very efficient technique for reducing the number of data points and for SNR improvement at relatively high frequencies and large delay times. But it is not suitable at low frequency noise and to improve the SNR at the beginning of the transient. However, the continuous time averaging [2] is a very convenient technique for above mentioned purposes. In addition, it has the advantage of allowing continuous transient display after each pulse and the size of the allocated memory buffer is independent of the number of averaged transients. The continuous time averaging mode is similar to the running average formed by a low-pass filter. Low-pass filter averages the data points consecutively in time so that low-pass filters can not be applied to the multiple times averaging. Multiple time averaging processes the whole set of transient data points in parallel, i.e. each data point is averaged with corresponding data points from the other transients which are at the same delay from the start of the transient. In this way the data points to be averaged are separated by one or more pulse periods and are not consecutive in time

Since the introduction of deep-level transient spectroscopy (DLTS) in 1974 by Lang [3], the method has been refined many times with new techniques for improving the sensitivity and accuracy, and for simplifying the measurement and data analysis procedures. At present, DLTS is comprised of a large group of different measurement techniques applied to a variety of test devices and materials. It is considered to be among the most accurate and reliable tools for investigating the properties of electrically active point defects in semiconductors [4].

Working principle of DLTS is based on some common features of all DLTS technique as: First, it is the time domain measurement of the emission of the charges trapped in electrically active centers. Second, this process is thermally activated and is based on Shockley-Read-Hall theory. Third, there is periodic alternation between filling of the traps with charge and emission of the trapped charge. This last feature is used for synchronized measurement and integration. This is the basic method used for signal recovery from noise in electronic instrumentation [5]. The DLTS experiment can be consisted of several steps. The first step is to detect the change of the trap occupancy with electrons as a measurable change in capacitance of the space charge region. The next steps are synchronous detection and averaging of this signal in order to improve the signal-to-noise ratio (SNR). There are two main approaches i.e. the use of analog or digital signal processing methods.

#### 4.3 Analog Methods

The noisy transient signal can be measured and integrated over many pulses using analog instruments such as a boxcar averager [6], a lock-in amplifier [7], or an exponential correlator [8]. In the classical setup, two boxcar channels are used to measure the signal at two different times in the transient, and these times define a time constant window of the instrumentation [9]. The averaging is performed by the boxcar channels and the difference versus the sample temperature is recorded, giving a DLTS spectrum. When the emission time constant of a deep level coincides with that of the instrumentation while scanning the temperature of the sample, the output signal indicates this coincidence with a peak in the spectrum. To apply the Arrhenius relationship to determine the energy level and the capture cross section of a trap, several temperature scans are needed using different settings of the time constant window of the instrumentation. Similarly, it is necessary to change the pulse frequency when using a lock-in amplifier, or the reference time constant when an exponential correlator is used, and to repeat the temperature scan in order to obtain enough data for the Arrhenius plot technique. In all these cases, the averaging technique simultaneously achieves two different goals - increasing the SNR and analyzing the transient parameters.

## 4.3.1 Advantages of Analog Methods

- Analog methods are simple to implement.

- Fast method.

- They produce an analog signal in real time.

- It is easy to plot this signal versus the temperature for spectrum-like curves

## 4.3.2 Disadvantages of Analog Methods

- One has to perform many temperature scans.

- · It can not resolve closely spaced energy levels of defects

- · It is difficult to do analysis of non-exponential transient

#### 4.4 Digital Methods

The digital methods record the whole transient as a set of data points. The noisy signal is first digitized and then processed using various digital techniques [10]. The transient parameter analysis can take place during the experiment, or data can be stored for later analysis. The transient can be analyzed using Spectral Analysis DLTS (SADLTS) [11-12], Fourier Transform Analysis [13-15], nonlinear least square fitting [16], the modulation function method [17], the method of moments [18-19], the correlation method of linear predictive modeling [20], or other digital methods described [21]. Since the whole transient is recorded, it is necessary to perform just one experimental temperature scan, which greatly reduces the time needed to perform the experiment.

## 4.4.1 Advantages of Digital Methods

- One has to perform just one temperature scan.

- It can resolve closely spaced energy levels of defects

- It has extensive possibilities for data analysis.

## 4.4.2 Disadvantages of Digital Methods

- It is not fast method as compare to analog method.

- Digital methods are not easy to implement

- The total numbers of stored data points are very large compare to analog methods.

• The greatest disadvantage of the digital method that is concerned with resolution of ADC, capacity of the memory buffer, and frequency of the testing pulse is explained as:

In digital method, the whole set of data points are recorded for the transient. Collection of data points depends on the resolution of 12-bit or 16-bit analog-to-digital converters (ADC) and frequency of the testing pulse. The 12-bit ADC has conversion time below  $10\mu$ s that is interfaced between analog output of capacitance meter and a PC. If 12-bit ADC in operated at frequency of 100 KHz, with the time interval between two data points is  $10\mu$ s for one degree interval over a temperature range of 50-350 K, then there are 131,072 sampling points which are stored into a 256 kilobyte buffer. From this large set of data, only 768 data points are selected and used, while the remaining 130,304 points are discarded. Second, after averaging, the buffer is cleared for processing of the new transient, and the old information is lost, thus making it more difficult to maintain high SNR. Third and most important, there is a substantial decrease in the SNR, especially in the tail of long transients, where the data point intervals are in the millisecond range, because the data points are selected from just 10 <sup>µ</sup>s long sampling intervals. In addition, recording of 768 data points for each degree in the 50 - 350 K range still requires almost 0.5 Mb disk space and Direct Memory Access (DMA) transfer into memory blocks larger than 64 Kbytes is complicated, since it requires continuous initialization of the DMA controller for crossing the memory page boundary [22].

This digital computerized DLTS can be divided into two parts:

(a) DLTS Hardware

(b) DLTS Software.

## 4.5 Hardware of Digital Computerized DLTS System

This digital computerized DLTS has following hardware:

- Capacitance Meter.

- Pulse Generator.

- Digital Multimeter

- Cryostat

- Oscilloscope

- PC

- Interfacing unit

- Coupling circuit

#### 4.5.1 Boonton Capacitance Meter

Boonton Capacitance Meter, Model 7200 is used to record the capacitance transients of the sample under the different sets of parameters in DLTS measurements. This versatile capacitance meter can measure the capacitance transients in digital and analog form. The Model 7200 is a microprocessor-based, fully automatic, and can measure upto 1MHz capacitance and loss measurements. Its capacitance range is 0 to 2000 pF, and its conductance range is 0 to 2000  $\mu$ S. The Model 7200 utilizes a 1 MHz test signal with programmable levels of 15, 30, 50, or 100 mV. It accepts, measure, display internal and external DC bias voltages over a range of  $\pm 100$  Volts and  $\pm 200$  volts respectively. Bias voltages of either polarity can be applied to the Hi terminals. This bias capability with fast responding C, G, and V outputs makes the instrument ideal for C-V or G-V plots, as well as DLTS studies. The Model 7200 uses a microprocessor with a fixed internal program for the automatic control of all measurements, computation, and display function. The use of microprocessor facilitates interfacing with advance technology extended (ATE) system. The Model 7200 is equipped with a full-function IEEE-488.2 bus interface. Functionality of the C-meter can be made versatile through programming using IEEE-488.2 bus interface Mnemonics. All front panel control function can be programmed, exception of the POWER ON and PLOT keys.

Response time of capacitance meter is 20 readings per second. So it takes 50 milliseconds for one reading. This is not a good response time because 2-points rate window can not be applied for frequency more than 10Hz. Bridge circuit of capacitance meter can not record capacitance more than this response. Efficiency of the capacitance can be improved if this bridge is bypassed and ADC of higher resolution is used.

Efficiency of the capacitance can also be improved using analog output through data acquisition card of better resolution.

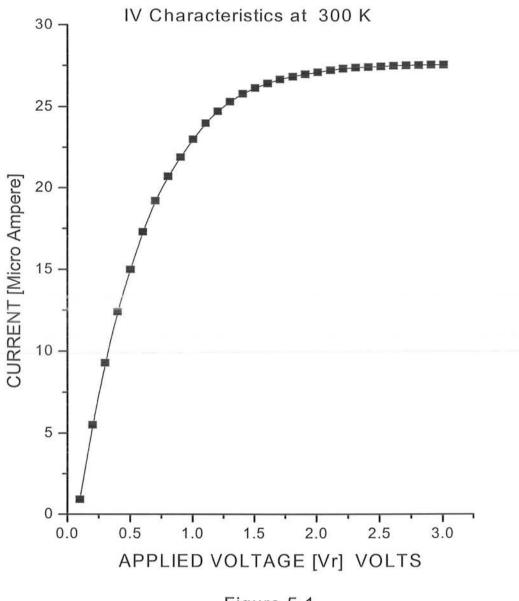

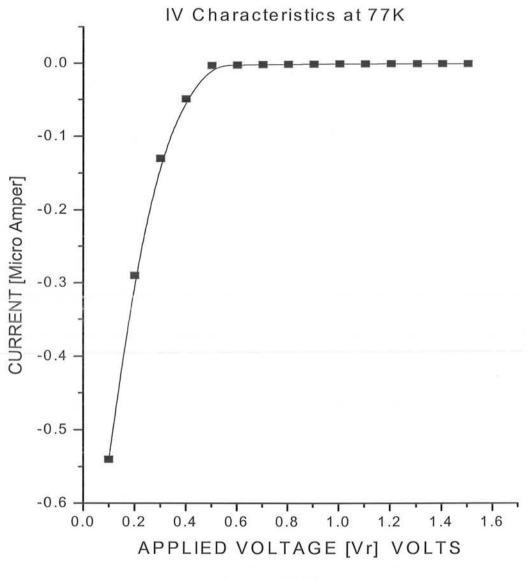

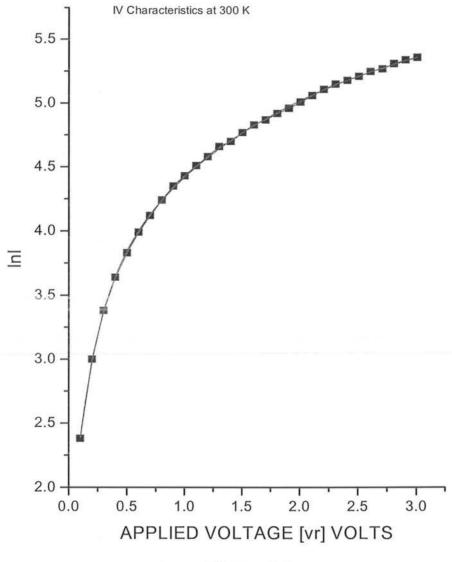

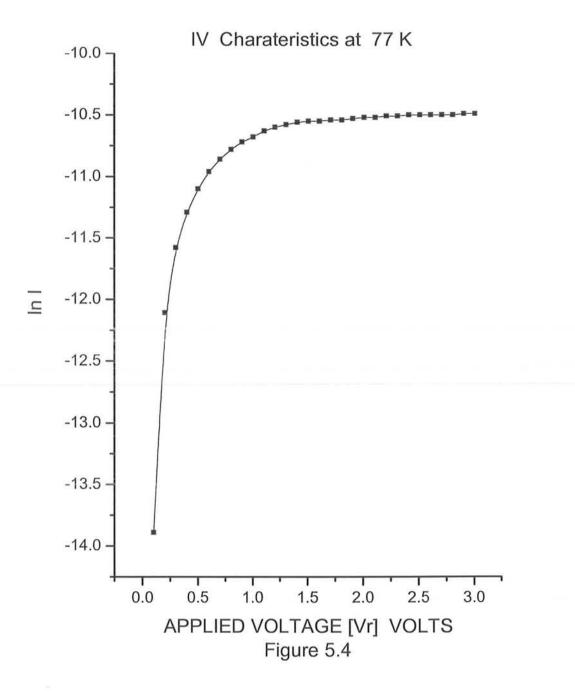

#### 4.5.2 Pulse Generator