# Capacitor-less LDO Design Techniques for Portable Applications in Nanometer CMOS

### Nadia Liaquat

Department of Electronics Quaid-i-Azam University, Islambad, Pakistan

A Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of

Master of Philosophy in Electronics

Sep, 2023

## DEPARTMENT OF ELECTRONICS QUAID-I-AZAM UNIVERSITY ISLAMBAD, PAKISTAN

A thesis entitled *Capacitor-less LDO Design Techniques for Portable Applications in Nanometer CMOS* by Nadia Liaquat in partial fulfilment of the requirements for the degree of Master of Philosophy, has been approved and accepted by the following,

> Supervisor Dr. Arshad Hussain Assistant Professor Department of Electronics Quaid-i-Aazam University Islamabad, Pakistan

> > Chairman

Dr. Qaisar Abbas Naqvi Professor Department of Electronics Quaid-i-Aazam University Islamabad, Pakistan Verily, in the creation of the heavens and the earth, and in the alternation of the night and the day, and in the ships (and vessels) which sail through the ocean carrying cargo profitable for the people, and in the (rain) water which Allah pours down from the sky, reviving therewith the earth to life after its death, and (the earth) in which He has scattered animals of all kinds, and in the changing wind directions, and in the clouds (that trail) between the sky and the earth, duty-bound certainly, (in these) are (many) signs for those who put their reason to work.

(Al-Baqarah: 164)

Dedicated to my parents .....

### Acknowledgements

I humbly thank Almighty Allah, the Compassionate, the Merciful, the most Glorious who gave me health, thoughts, affectionate parents, talented teachers, helping friends, and an opportunity to contribute to the ever-evolving self-perceived form of vast human knowledge.

First, I am deeply grateful to my supervisor, Dr. Arshad Hussain, for his exceptional guidance, expertise, and unwavering commitment to excellence throughout my research.

I am also indebted to my parents and siblings, Wasif Liaquat and Sadia Liaquat, for their unconditional love and support. Your sacrifices and encouragement have been the bedrock upon which I built my academic pursuits. Thank you for the unwavering support and encouragement throughout my academic pursuits.

This acknowledgment can't be considered complete until I thank some of my good friends Saba, Usama, Mudassar, Farrukh, Zeeshan, Saira, Sehrish and Maimona, with whom I have had fruitful discussions related to my work. I'd like to extend a special thanks to Nadia Afzal and Amna Khalid for their invaluable assistance and support in my research. I would like to express my sincere gratitude to my senior, Sohail Ahmed, for his invaluable guidance and support in my research.

> Nadia Liaquat Sept 5, 2023

#### Abstract

In the realm of modern electronics, effective power management is crucial, especially with the prevalence of System-on-Chip (SoC) technologies. Traditional Low-Dropout Voltage Regulators (LDOs) often rely on output capacitors, which can incur additional costs, increase board sizes, and expand pin counts. This study focuses on the development of two external capacitor-less Low-Dropout Voltage Regulator (LDO) designs in 55nm CMOS technology for portable applications. The first LDO design spans a voltage range of 1 to 4 V, maintaining a stable 1.2 V output across loads from 0.2 to 50 mA, with a power consumption of 1 mW only. Using a Transient Enhancement Circuit, It exhibits minimal voltage spikes (below 150 mV), a 0.1 us settling time, and a quiescent current of 59  $\mu$ A under maximum load. The second LDO design integrates a slew rate enhancement circuit for improved transient responses. It remains stable throughout a 0–50 mA full load range without an output capacitor. The LDO's output voltage recovers within 0.4  $\mu$ s with a voltage spike of less than 40 mV, demonstrating enhanced DC load control (0.031 mV/mA) consuming  $71\mu$ W. It operates with a quiescent current of 22  $\mu$ A and a 200 mV dropout voltage at 1V supply Voltage and regulate the circuit output Voltage at 0.8V. Both LDOs offer efficient load and line transient responses, reduced settling times, and resilience to process, voltage, and temperature variations, ensuring consistent and reliable performance.

# Contents

| Contents |                 |          | vii                                       |      |

|----------|-----------------|----------|-------------------------------------------|------|

| Li       | List of Figures |          |                                           | x    |

| Li       | st of           | Tables   |                                           | xii  |

| A        | bbrev           | viations | S                                         | xiii |

| 1        | Intr            | oductio  | on                                        | 1    |

|          | 1.1             | Powe     | r Management Unit (PMICs)                 | 3    |

|          |                 | 1.1.1    | Switching Regulators / DC-DC converter    | 4    |

|          |                 | 1.1.2    | Linear Regulator                          | 5    |

|          |                 | 1.1.3    | Comparison                                | 7    |

|          |                 | 1.1.4    | Low Drop Out (LDO) Regulator              | 8    |

|          | 1.2             | Funda    | amental Structure/Design Elements         | 10   |

|          |                 | 1.2.1    | Error Amplifier:                          | 10   |

|          |                 | 1.2.2    | Pass Transistor                           | 11   |

|          |                 | 1.2.3    | Reference Voltage                         | 12   |

|          |                 | 1.2.4    | Resistive Feedback Network                | 13   |

|          | 1.3             | Opera    | ation                                     | 13   |

|          | 1.4             | LDO      | Linear Regulator Characterization         | 15   |

|          |                 | 1.4.1    | Static-state Specifications               | 15   |

|          |                 | 1.4.2    | Dynamic-state Specifications:             | 18   |

|          |                 | 1.4.3    | High Frequency Specifications:            | 20   |

|          | 1.5             | Motiv    | vation and Objectives for Designing LDOs: | 23   |

#### **CONTENTS**

| 5 | Con        | clusion                                                        | 73       |

|---|------------|----------------------------------------------------------------|----------|

|   | 4.5        | Comparison                                                     | 71       |

|   | 4.4        | Experimental Results and Discussion                            | 67       |

|   | 4.3        | Reducing Overshoot and Undershoot                              | 65       |

|   | 4.2        | Circuit Realization and Schematic                              | 64       |

|   |            | 4.1.2 Analysis of stability and design constraints             | 58       |

|   |            | 4.1.1 Implemented Topology                                     | 57       |

|   | 4.1        | LDO architecture                                               | 57       |

|   |            | cement                                                         | 56       |

| 4 | -          | acitor-Less LDO Voltage Regulator Design Using Slew-rate En-   |          |

|   | 6          |                                                                |          |

|   | 3.10       | Achieved results                                               | 54       |

|   | 3.9        | Line Regulation                                                | 53       |

|   | 3.8        | AC and Stability Analysis                                      | 52       |

|   |            | 3.7.1 DC Analysis                                              | 50       |

|   | 3.7        | Simulation and Result Analysis                                 | 50       |

|   | 3.6        | Design Specification                                           | 49       |

|   | 3.5        | Simulation Environment                                         | 49       |

|   | 3.4        | Transient Response                                             | 46       |

|   | 3.3        | Design Challenges                                              | 44       |

|   | 3.2        | The fundamental structure:                                     | 42       |

|   | 3.1        | Studied LDO Architecture                                       | 39       |

|   |            | ot and overshoot                                               | 39       |

| 3 | Capa       | acitor-Less Low Voltage Regulator Design with optimized under- |          |

|   | 2.0        |                                                                | 32       |

|   | 2.4<br>2.5 | Internal Compensation                                          | 30<br>32 |

|   | 2.3<br>2.4 | External Compensation                                          | 29<br>30 |

|   | 2.2        | Frequency compensation                                         | 29       |

|   | 2.1        | AC Stability                                                   | 28       |

| 2 |            | e-of-the-Art                                                   |          |

| ſ |            |                                                                | 27       |

|   | 1.6        | Thesis Organization                                            | 25       |

### Bibliography

75

# **List of Figures**

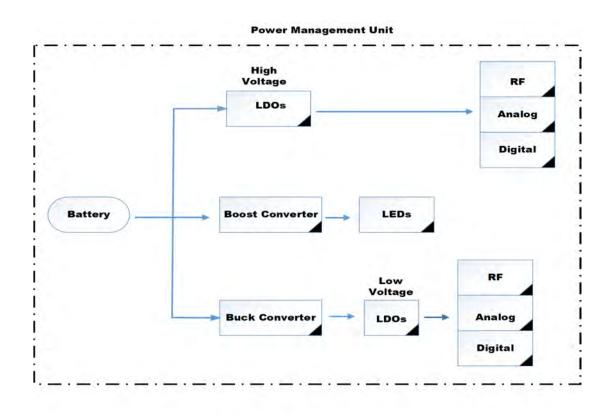

| 1.1  | Power management unit block                                       | 2  |

|------|-------------------------------------------------------------------|----|

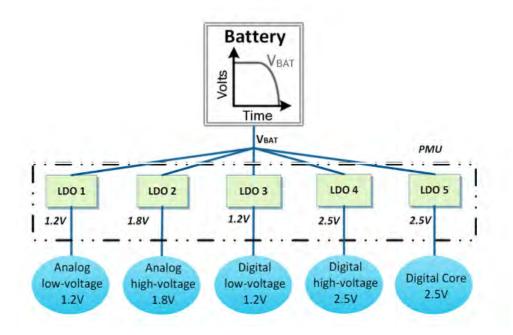

| 1.2  | Power management Unit with several LDOs (Low Dropout)             | 3  |

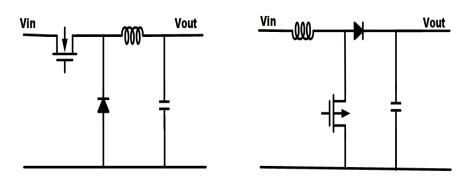

| 1.3  | Buck and Boost converter topologies                               | 5  |

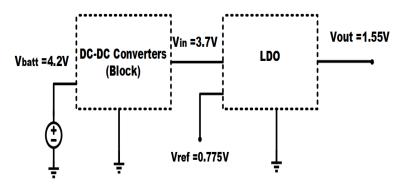

| 1.4  | Good linear efficiency regulation                                 | 5  |

| 1.5  | Linear Regulator                                                  | 6  |

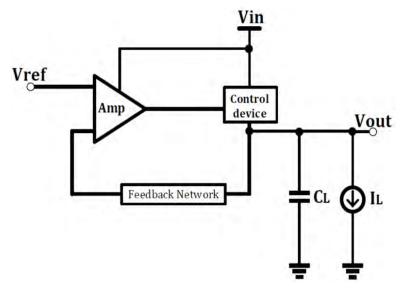

| 1.6  | LDO regulator (low dropout)                                       | 8  |

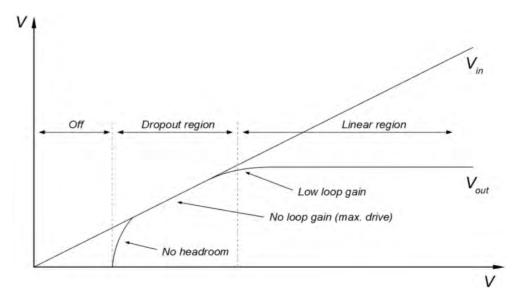

| 1.7  | LDO voltage regulator input-output voltage characteristics        | 9  |

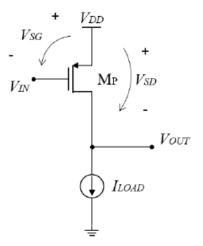

| 1.8  | Pass Transistor design                                            | 12 |

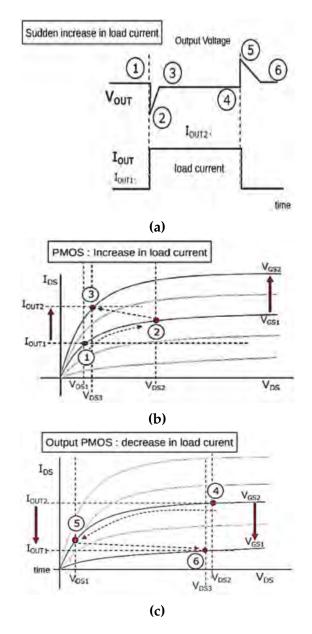

| 1.9  | (a), (b), (c) in LDO working                                      | 14 |

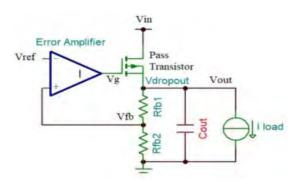

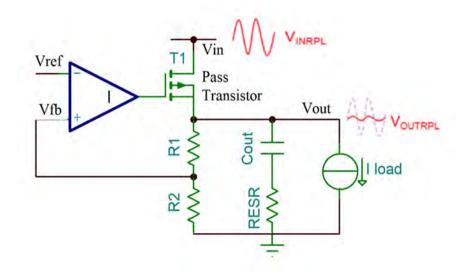

| 1.10 | PMOS based LDO                                                    | 15 |

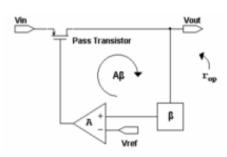

| 1.11 | Closed Loop system                                                | 15 |

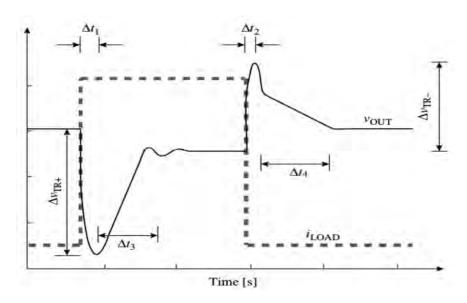

| 1.12 | Typical transient reaction to sudden load current changes         | 19 |

| 1.13 | A simple LDO architecture                                         | 22 |

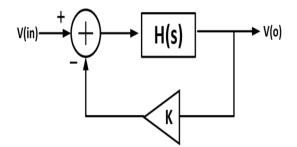

| 2.1  | Typical Feedback System                                           | 28 |

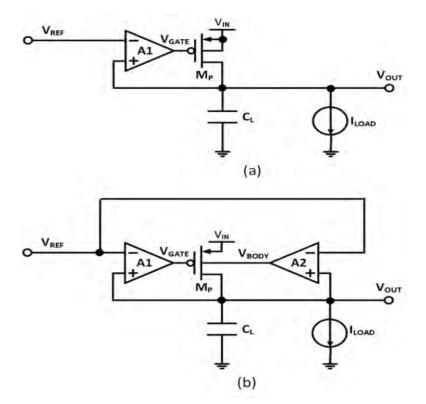

| 2.2  | Schematic of LDO with unity gain feedback: : without body bias    |    |

|      | control                                                           | 29 |

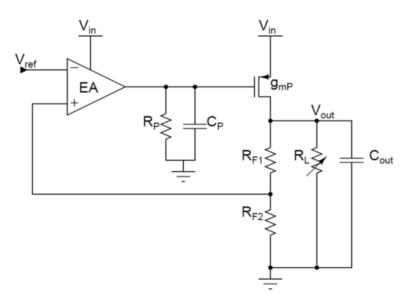

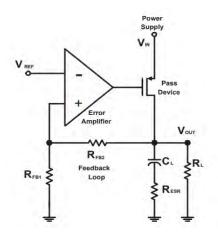

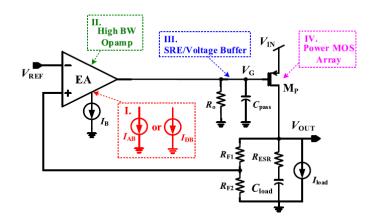

| 2.3  | LDO Voltage Regulator Scheme                                      | 31 |

| 2.4  | Schematic of LDO with unity gain feedback: : (a) without body     |    |

|      | bias control and (b) with bulk-modulation.                        | 35 |

| 2.5  | Typical circuit techniques for fast-transient LDO design          | 37 |

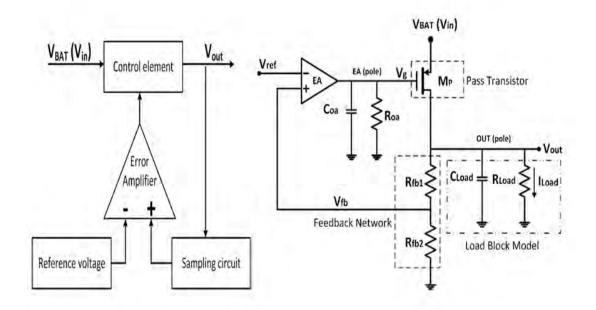

| 3.1  | (a) Linear regulator conceptual scheme (b) A simplified schematic |    |

|      | of a CMOS low-dropout (LDO) regulator                             | 40 |

#### LIST OF FIGURES

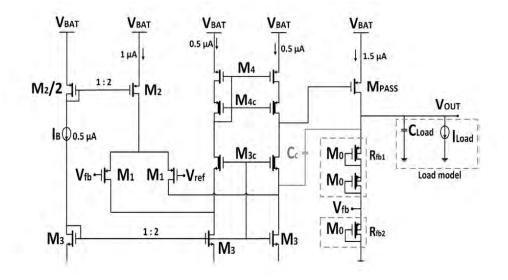

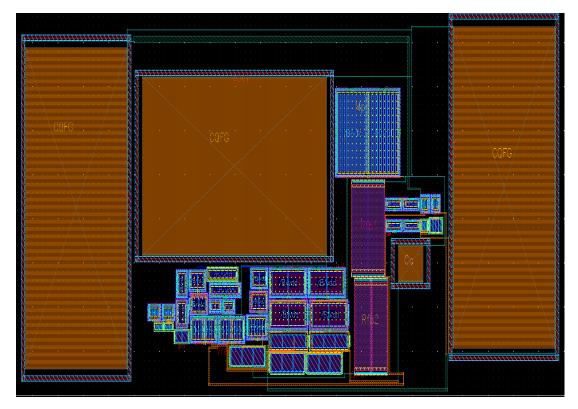

| The fundamental architecture of the CMOS low-dropout (LDO)                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| regulator designed for generating a 1.2V output                                                                                                                                                                                                                                                          | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Characteristics of Transistors                                                                                                                                                                                                                                                                           | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

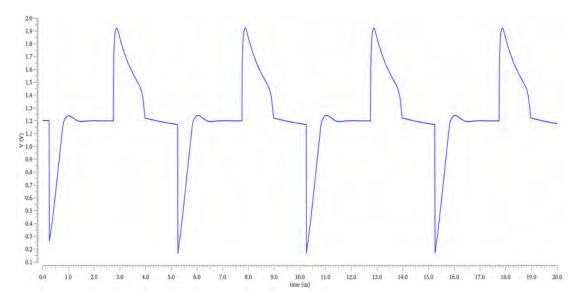

| Transient behavior of the load, between 0 to 50 mA, with VBAT                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| = 3 V and no transient augmentation                                                                                                                                                                                                                                                                      | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

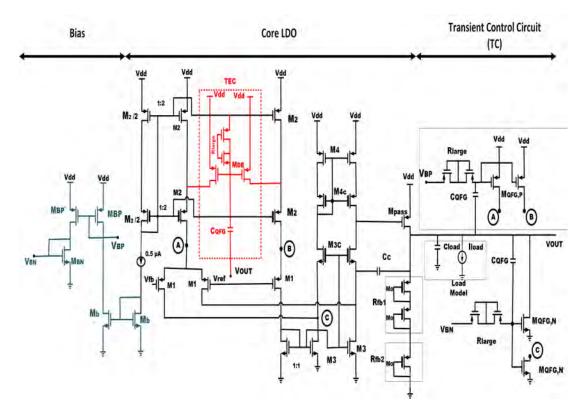

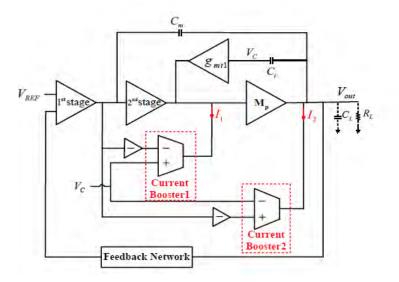

| Low dropout regulator core construction with transient control                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| circuitry                                                                                                                                                                                                                                                                                                | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

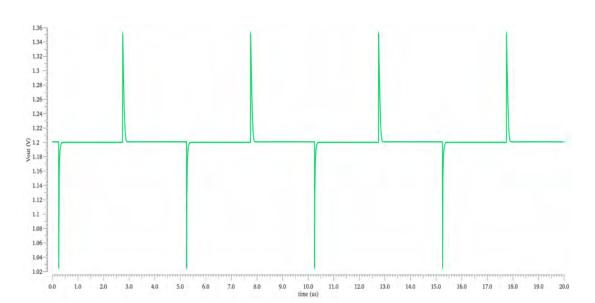

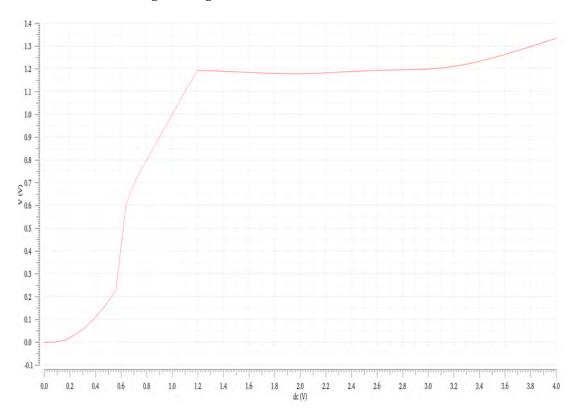

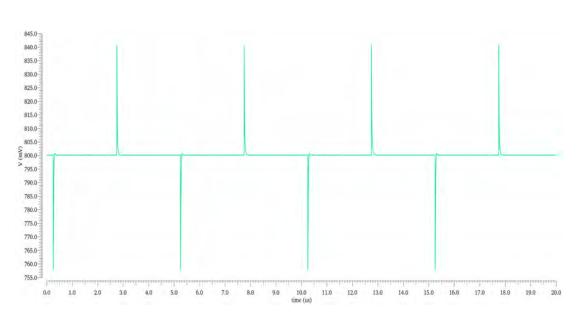

| : Measured Output Voltage of the LDO Regulator with C=0 pF                                                                                                                                                                                                                                               | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

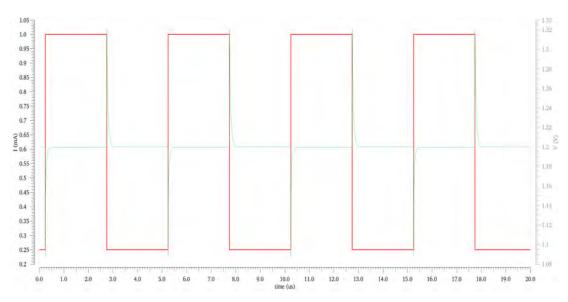

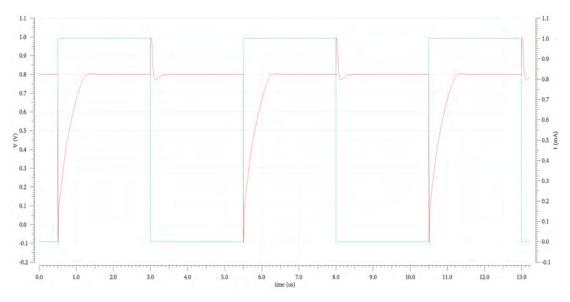

| LDO transient response and lout on the load step from 50mA to                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10mA                                                                                                                                                                                                                                                                                                     | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

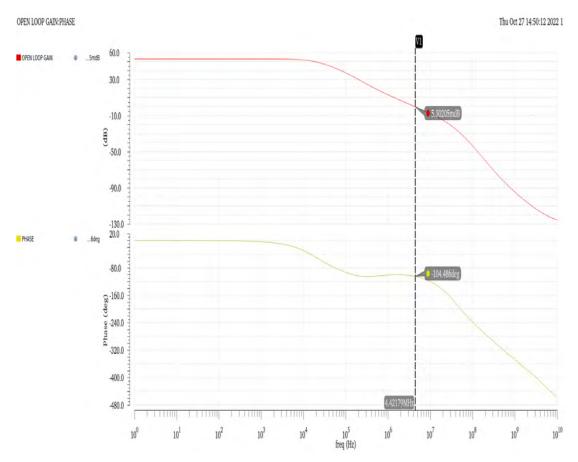

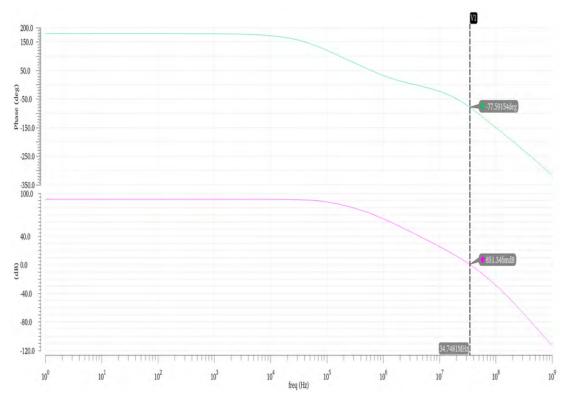

| Frequency response of the single stage error amplifier                                                                                                                                                                                                                                                   | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

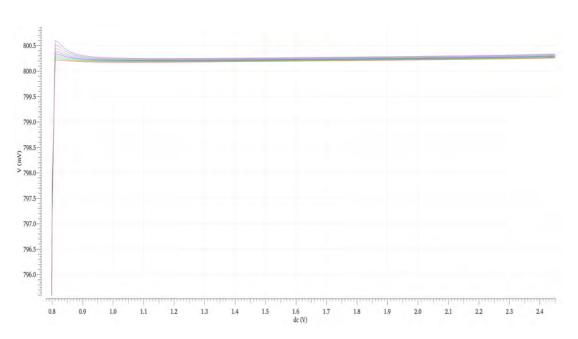

| Simulated line-transient response with a 0pF off-chip capacitor                                                                                                                                                                                                                                          | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

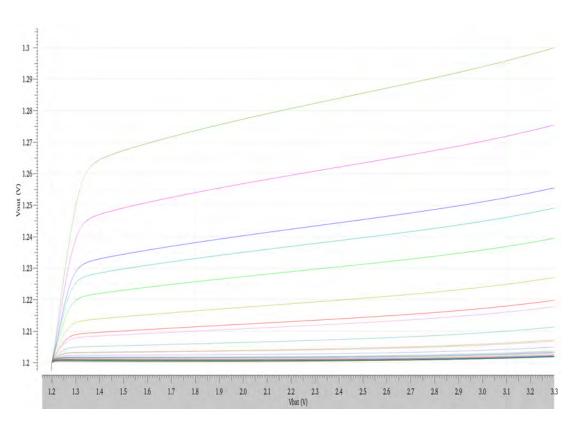

| Line transient simulation results for Temperature change from                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| -40° to 120° and IL=1mA with CL=0 pF                                                                                                                                                                                                                                                                     | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

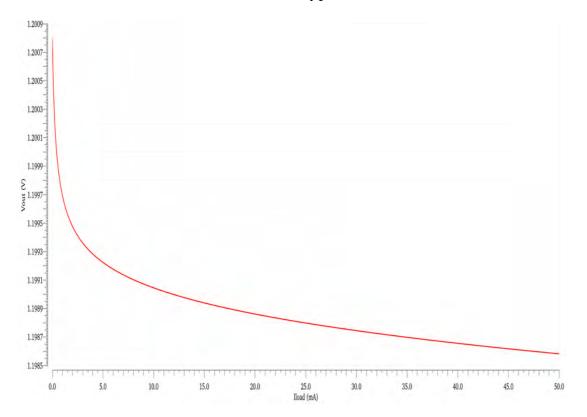

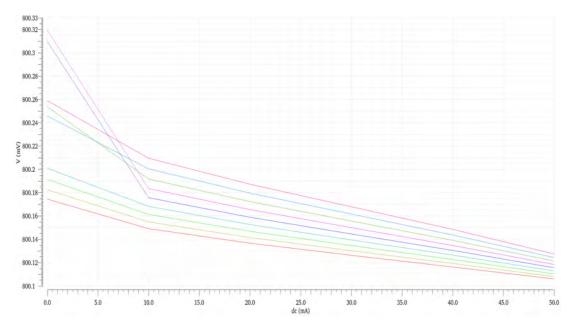

| Simulated load-transient response with a 0pF off-chip output                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| capacitor for different current changes $\Delta$ Iload=0 to 50mA                                                                                                                                                                                                                                         | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

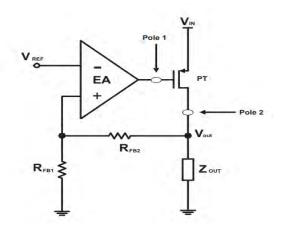

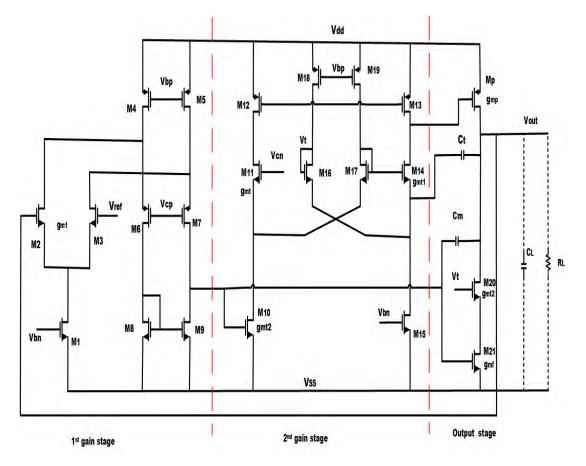

| Basic Structure of the OCL-LDO regulator                                                                                                                                                                                                                                                                 | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                          | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

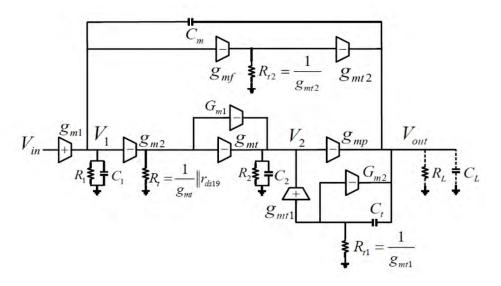

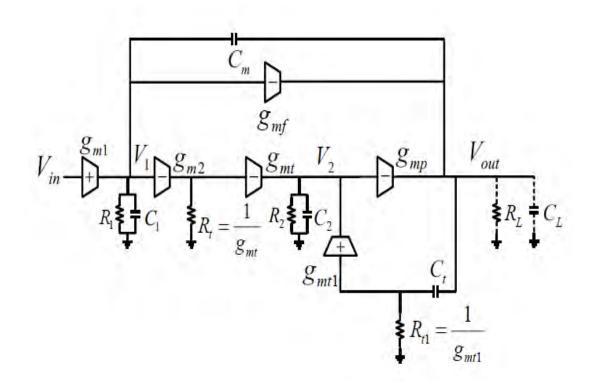

| Small Signal model of the OCL-LDO regulator                                                                                                                                                                                                                                                              | 58<br>59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Small Signal model of the OCL-LDO regulator                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                          | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

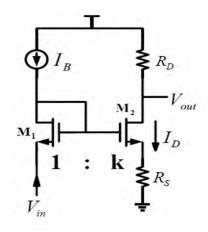

| Equivalent transconductance cell (Gm) model                                                                                                                                                                                                                                                              | 59<br>60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Equivalent transconductance cell (Gm) model                                                                                                                                                                                                                                                              | 59<br>60<br>61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Equivalent transconductance cell (Gm) model                                                                                                                                                                                                                                                              | 59<br>60<br>61<br>65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |