# Design and Development of Serial RISC-V Soft ELE Microprocessor Core

Supervisor: Dr.Aqeel Abbas Department of Electronics Qau

Co Supervisor: Dr.Rehan Ahmed Seecs Nust

By

# Abdur Rehman M.Ashraf September-2023-Mphill-Ele

A thesis submitted in partial fulfillment of the requirements for the degree of Masters of Philosophy in Electronics (Mphill Ele)

In

Department of Electronics, Quaid I Azam University Islamaabd, Pakistan.

(September 2023)

# **Thesis Acceptance Certificate**

Certified that final copy of MPhil thesis entitled "Design and Development of Serial RISC-V Soft Microprocessor Core" written by Abdur Rehman, (Registration No 02102113013), of Department of Electronicshas been vetted by the undersigned, found complete in all aspects as per QAU Statutes/Regulations, is free of plagiarism, errors and mistakes and is accepted as partial fulfillment for award of MPhil degree.

Signature: Supervisor: Dr.Aqeel Abbas Date: \_

Signature:

Co Supervisor: Dr.Rehan Ahmed

Date: 21st March 2024

Signature (HoD): Date:

# Approval

It is certified that the contents and form of the thesis entitled "Design and Development of Serial RISC-V Soft Microprocessor Core" submitted by Abdur Rehman have been found satisfactory for the requirement of the degree.

| Supervisor | Dr.Aqeel Abbas |

|------------|----------------|

| Signature: | April          |

| Date       |                |

| Co Su   | pervisor: Dr.Rehan Ahmed |

|---------|--------------------------|

| Signati | ire: (Klung.             |

| Date:   | 21st March 2024          |

# Dedication

I dedicate this thesis to my beloved parents, Muhammad Ashraf and Shahnaz Begum, my siblings, my teachers, my friends and to all the deserving children who do not have access to quality education, especially young girls.

# **Certificate of Originality**

I hereby declare that this submission is my own work and to the best of my knowledge it contains no materials previously published or written by another person, nor material which to a substantial extent has been accepted for the award of any degree or diploma at Department of Electronics QAU or at any other educational institute, except where due acknowledgement has been made in the thesis. Any contribution made to the research by others, with whom I have worked at Integrated Cicuit Design Lab NUST or elsewhere, is explicitly acknowledged in the thesis. I also declare that the intellectual content of this thesis is the product of my own work, except for the assistance from others in the project's design and conception or in style, presentation and linguistics which has been acknowledged.

Author Name: Abdur Rehman M.Ashraf

Signature: (12chman

# Acknowledgments

Glory be to Allah (S.W.A), the Creator, the Sustainer of the Universe. There is no power except Allah and HE is the only one who has the power to honor whom HE pleases and to abase whom HE pleases. Verily no one can do anything without HIS will. I bear witness that there is no worthy of worship except ALLAH, the one alone, without a partner and I bear witness that MUHAMMAD (S.A.W.W) is his servant and Messenger. From the day, I came to QAU till the day I came to NUST and now writing this thesis, He was the only one Who blessed me and opened ways for me and showed me the path to success. There is nothing that can payback for His bounties throughout my research period to complete it successfully.

I pay my appreciation to my Advisor Dr.Muhammad Aqeel Abbas who permitted me to conduct my research in the field I choose. And always stood with me in my decisions and guided me throughout my research period.

And now I extend my heartfelt gratitude to the three invaluable gems in my life. [1] My coadvisor Dr.Rehan Ahmed and his two senior research assistants [2] Qazi Shahid Ullah and [3] Shaheer Sajid. They have been a wellspring of inspiration all through this research and above all, during my Mphill thesis. They have consistently been an astounding pioneer and guide. Their reliability, flexibility, and dedication have left a persuasive impact on my character. Without there understanding and difficult work, I would not have the option to finish my research program. And how I overlook the deadlines set by my Co-Advisor Dr.Rehan Ahmed they stand as a wellspring of motivation for me.

Abdur Rehman M.Ashraf

# Contents

| 1 | Intre | oduction and Motivation                  | 1  |

|---|-------|------------------------------------------|----|

|   | 1.1   | Objectives                               | 2  |

|   | 1.2   | Significance                             | 2  |

|   | 1.3   | Background and Motivation                | 3  |

|   | 1.4   | Problem Statement and Contribution       | 3  |

| 2 | Lite  | erature Review                           | 5  |

|   | 2.1   | Microprocessor Architecture              | 5  |

|   |       | 2.1.1 Evolution of Microprocessors       | 5  |

|   |       | 2.1.2 Instruction Set Architecture (ISA) | 6  |

|   |       | 2.1.3 Data and Control Paths             | 6  |

|   |       | 2.1.4 Instruction Execution              | 6  |

|   | 2.2   | Challenges in Microprocessor Design      | 6  |

|   | 2.3   | Bit-Serial Execution                     | 7  |

|   |       | 2.3.1 Advantages and Limitations         | 8  |

|   | 2.4   | RISC-V Instruction Set Architecture      | 9  |

| 3 | Des   | sign and Methodology                     | 11 |

|   | 3.1   | Types of Instructions                    | 11 |

|   | 3.2   | Addressing Modes                         | 12 |

|   | 3.3   | Architectural Overview                   | 16 |

### CONTENTS

|   | 3.4 | 3it-Serial Data Path Design                | .8 |

|---|-----|--------------------------------------------|----|

|   | 3.5 | Design Consideration for Energy Efficiency | 20 |

|   |     | 3.5.1 Serial Execution:                    | 20 |

|   |     | 3.5.2 Instruction Pipelining               | 21 |

| 4 | Imp | ementations Details 2                      | 3  |

|   | 4.1 | Pipelining                                 | 23 |

|   | 4.2 | Load/Store Unit                            | 24 |

|   | 4.3 | Register File to Register File             | 25 |

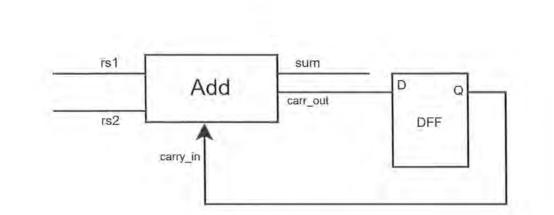

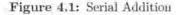

|   |     | 4.3.1 Addition:                            | 25 |

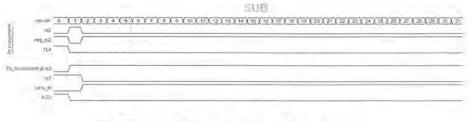

|   |     | 4.3.2 Subtraction:                         | 26 |

|   |     | 4.3.3 Logical Operations:                  | 28 |

|   |     | 4.3.4 Shift Right Arithmetic (SRA):        | 28 |

|   |     | 4.3.5 Shift Right Logical (SRL)            | 29 |

|   |     | 4.3.6 Shift Left Logical (SLL)             | 29 |

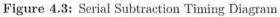

|   |     | 4.3.7 Set Less Then(SLT)                   | 30 |

|   |     | 4.3.8 Set Less Then Unsigned (SLTU)        | 31 |

|   |     | 4.3.9 Load Word (LW)                       | 31 |

|   |     | 4.3.10 Load Half Word (Lh)                 | 32 |

|   |     | 4.3.11 Load Byte (Lb)                      | 33 |

|   |     | 4.3.12 Load Upper Immediate                | 33 |

|   |     | 4.3.13 Add Upper Immediate to Pc (AUIPC)   | 33 |

|   | 4.4 | Register File to Memory                    | 34 |

|   |     | 4.4.1 Store Word (Sw)                      | 34 |

|   |     | 4.4.2 Store Half (Sh)                      | 34 |

|   |     | 4.4.3 Store Byte (Sb)                      | 34 |

|   | 4.5 | Control Flow                               | 35 |

|   |     | 4.5.1 Jump and Link (JAL)                  | 37 |

|   |     |                                            |    |

|   |     | 4.5.2     | Jump and Link Register (JALR) $\ ,\ \ldots\ \ldots\ \ldots\ \ldots\ \ldots\ \ldots\ \ldots\ \ldots$ | 37 |

|---|-----|-----------|-----------------------------------------------------------------------------------------------------|----|

|   |     | 4.5.3     | Branch If Equals to Zero (BEQ)                                                                      | 38 |

|   |     | 4.5.4     | Branch if Not Equal to Zero (BNE)                                                                   | 39 |

|   |     | 4.5.5     | Branch Greater than Equal to (BGE)                                                                  | 39 |

|   |     | 4.5.6     | Branch Greater Then Equal to Unsigned(BGEU)                                                         | 40 |

|   |     | 4.5.7     | Branch Less Then (BLT)                                                                              | 40 |

|   |     | 4.5.8     | Branch Less Then Unsigned (BLTU)                                                                    | 40 |

|   | 4.6 | Data I    | Path                                                                                                | 41 |

|   | 4.7 |           | architecture                                                                                        | 42 |

|   | 4.8 | Hazar     | d Unit                                                                                              | 43 |

|   |     | 4.8.1     | Structural Hazards:                                                                                 | 43 |

|   |     | 4.8.2     | Data Hazards:                                                                                       | 43 |

|   |     | 4.8.3     | Control Hazard:                                                                                     | 43 |

|   |     | 4.8.4     | Handling of Structural Hazards                                                                      | 44 |

|   |     | 4.8.5     | Handling of Data Hazards                                                                            | 44 |

|   |     | 4.8.6     | Handling Control Hazard                                                                             | 44 |

|   | 4.9 | Progr     | amming and Tools                                                                                    | 45 |

|   |     | 4.9.1     | Tools                                                                                               | 45 |

|   |     | 4,9.2     | Programming                                                                                         | 45 |

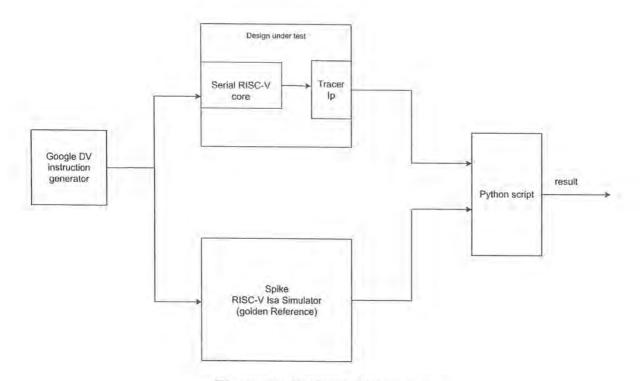

| 5 | Vor | rificatio |                                                                                                     | 46 |

| Ű | ver | 5.0.1     | GOOGLE DV Instruction Generator                                                                     |    |

|   |     | 5.0.2     | Design Under Test (DUT)                                                                             |    |

|   |     | 5.0.2     | Spike                                                                                               |    |

|   |     | 5.0.4     | Python Script                                                                                       |    |

|   |     | 0.0.4     | rython Script                                                                                       | 41 |

| 6 | An  | alysis    | And Results                                                                                         | 51 |

|   | 6.1 | FPG.      | A Implementation                                                                                    | 51 |

|   |     |           |                                                                                                     |    |

# CONTENTS

| UART   | ' Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

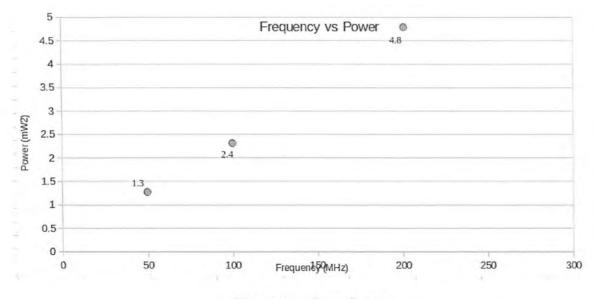

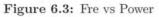

| Power  | Performance Area (PPA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.3.1  | Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6.3.2  | Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6.3.3  | Area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| clusio | n and Future Works 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Conclu | usion $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Future | e Works                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7.2.1  | Enhanced Architectural Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.2.2  | Mixed Bit-Serial and Parallel Architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 7.2,3  | Multi core Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7.2.4  | Advanced Verification and Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1.2.4  | Additional of the second |

|        | Power<br>6.3.1<br>6.3.2<br>6.3.3<br>clusio<br>Concl <sup>1</sup><br>Future<br>7.2.1<br>7.2.2<br>7.2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

# List of Figures

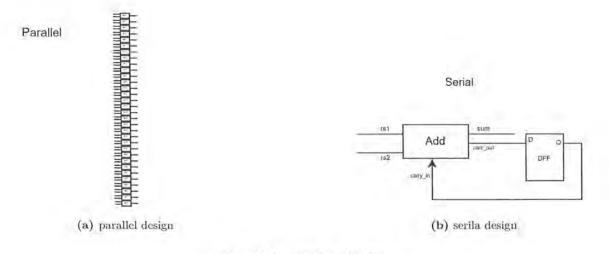

| 2.1  | Serial vs Parallel                      | 7  |

|------|-----------------------------------------|----|

| 3.1  | Conventional Parallel Branching         | 14 |

| 3.2  | Parallel Load Instruction               | 15 |

| 3.3  | Parallel Store Instruction              | 16 |

| 4.1  | Serial Addition                         | 26 |

| 4.2  | Serial Subtraction                      | 27 |

| 4.3  | Serial Subtraction Timing Diagram       | 27 |

| 4.4  | Serial Logical Operations               | 28 |

| 4.5  | Shift Right Logical                     | 29 |

| 4.6  | Serial Set Less Then Timing Diagram     | 31 |

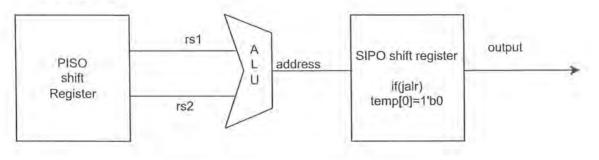

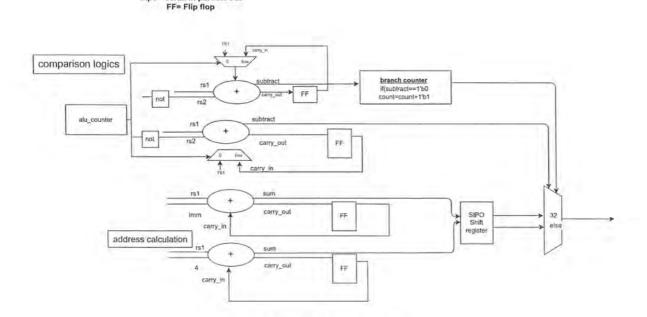

| 4.7  | Serial Jump and Link Register           | 38 |

| 4.8  | Serial Branch Prediction                | 41 |

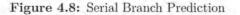

| 4.9  | Serial Branch Prediction Timing Diagram | 41 |

| 4.10 | Serial Branch Prediction                | 42 |

| 5.1  | Verification Environment                | 48 |

| 5.2  | Instruction Generator                   | 48 |

| 5.3  | Spike Result (Golden Reference)         | 49 |

| 5.4  | Bit-Serial Core Result                  | 49 |

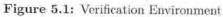

| 5.5  | Questa Sim Simulation                   | 50 |

### LIST OF FIGURES

141

| LIST OF | IGURES         |

|---------|----------------|

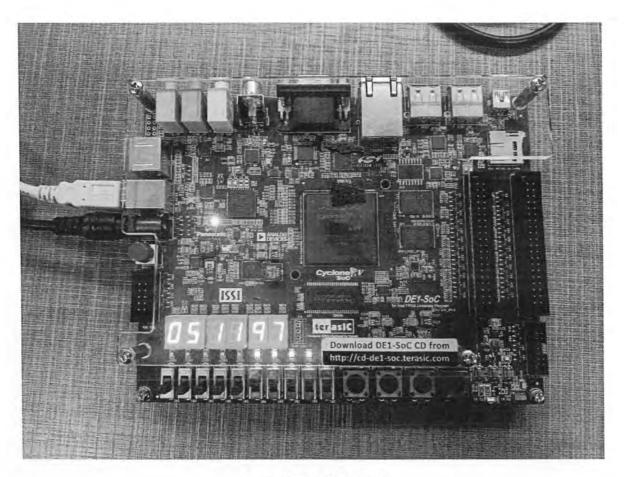

| 6.1     | PGA Demo       |

| 6.2     | art Test       |

| 6.3     | re vs Power    |

| 6.4     | re vs Area     |

| 8.1     | lagrism report |

# List of Tables

| 2.1 | RISC-V ISA                            | ) |

|-----|---------------------------------------|---|

| 3.1 | Operation count Parallel vs Serial    |   |

| 4.1 | Signed Arithmetic Rules               | ) |

| 4.2 | Sign Extension                        | 2 |

| 4.3 | Tools,                                | j |

| 6.1 | LUTS and Register Utilization in FPGA | L |

| 6.2 | Frequency Power and Area              | 1 |

# Abstract

It's a fact! That in modern microprocessor designs, energy efficiency and performance are two critical factors that drive research and innovation. As traditional approach to design the microprocessor has employed parallel processing techniques to enhance performance, but such approach often come with high power and area consumption. In recent few decades, we witnessed the remarkable advancement in microprocessor deign leading to increased computational power and energy efficiency in modern computing system. Therefore, the investigation of innovative architectures that utilize bit-serial processing approach is an important field of research in processor design. This thesis work presents the design, implementation, and performance evaluation of a bit-serial approach to design a 32-bit RISC-V microprocessor. Aiming to leverage the benefits of bit-serial processing. The proposed microprocessor deign execute the RISC-V instructions using bit-serial execution (one-bit per clock edge). This technique substantially reduce hardware complexity, increased energy efficiency and achieve higher clock frequency. The proposed microprocessor is pipelined and covered almost all the data, control and structural hazards. This design is made by using Hardware descriptive language name Verilog. And duly verified using Google Design Verification Environment. And its performance evaluation is conducted. Through a comprehensive set of benchmarks to compare the bit-serial RISC-V microprocessor against with the conventional RISCV microprocessor and state of the art microarchitectures. The benchmarks encompass diverse work loads, including integer arithmetic, memory access, and control intensive tasks. Matrices such as power consumption, throughput, energy efficiency and area efficiency are considered to assess the effectiveness of the proposed architecture.

# CHAPTER 1

# Introduction and Motivation

In today's rapidly advancing technological landscape, microprocessor designs are continuously playing a pivotal role in shaping computing system's performance and energy efficiency. In the relentless pursuit of energy efficiency, and more faster computing systems, microprocessor architectures have evolved significantly over the past few years. With the constant demand for reduced power consumption and higher computing power, we the researchers are continuously exploring innovative architectures for microprocessors to meet these challenges. For this, one such novel and potential alternative approach to traditional parallel processing is the bit-serial technique, Which offers us the potential for energy-efficient executions while adhering to the open-source RISC-V instruction set architecture (ISA).

In 2010 at the University of California, Berkeley the new instructions set architecture (ISA) was developed. The royalty-free and open-source RISC-V instruction set architecture (ISA) gained prominence due to its flexible and adaptable framework for a wide range of computing devices. The purpose of developing the open-source and extensible instruction set is not only for academic use but also for commercial products. Remember that it is sometimes referred to as the "Linux" of processors. As a consequence, RISC-V received significant support from the open-source community, due to the adaptation and development of programming tools, such as GCC compiler with GFB support, GNU MCU Eclipse, LLVM toolchain, C libraries, and an official ISA simulator (spike).

In terms of the operating system, it has already support for FreeBSD, Linux Kernal, and ports of Debian. Due to this, the list of RISC-V members includes big companies such as NVIDIA, GOOGLE, Western Digital, Samsung, and Qualcomm. And currently Western Digital and Nvidia are working on their RISC-V microcontrollers to incorporate them in their commercial

#### CHAPTER 1: INTRODUCTION AND MOTIVATION

products, as an alternative to their current solutions.

This thesis delves into the design, implementation, and evaluation of a Bit-Serial RISC-V Microprocessor, aiming to leverage the advantages of bit-serial execution while adhering to the widely adopted RISC-V ISA. Bit-serial execution is a unique approach that executes data one bit per clock edge, in contrast to conventional parallel execution, which handles whole vector simultaneously. By executing data serially, bit-serial architectures can potentially achieve reduced hardware complexity and greater energy efficiency.

The introductory chapter of this thesis lays the foundation for understanding the motivations, objectives, and significance of the research conducted. It presents the rationale behind exploring bit-serial processing, discusses the current challenges in microprocessor design, and provides an overview of the key contributions and organization of the thesis.

## 1.1 Objectives

The primary objective of this thesis is to design and implement a Bit-Serial RISC-V Microprocessor that explores the feasibility of bit-serial execution within the context of the RISC-V instruction set architecture. Specific goals include:

1. Developing bit-serial Datapath, execution unit, and memory subsystem tailored to the RISC-V ISA.

2. Investigating the strengths and limitations of the bit-serial processing technique for different types of workloads and applications.

3. Evaluating the energy efficiency and performance of the Bit-Serial RISC-V Microprocessor against conventional RISC-V processors and state-of-the-art microarchitectures through extensive benchmarking.

### 1.2 Significance

The significance of this research lies in its potential to pave the way for more energy-efficient microprocessor architectures. If bit-serial processing demonstrates promising advantages over traditional parallel processing for certain workloads, it could be an essential step toward addressing the energy consumption challenges in computing systems. Additionally, the implementation of a Bit-Serial RISC-V Microprocessor could open new avenues for exploration in the design of

#### Chapter 1: Introduction and Motivation

future energy-efficient processors.

### 1.3 Background and Motivation

Traditional parallel execution techniques have long been the backbone of microprocessor design, enabling high-performance gains and throughput through the simultaneous processing of multiple data elements. However, as microprocessors have grown more complex, power consumption and area have become a major concern, particularly in battery-powered devices and data centers. This has prompted us to seek novel approaches that strike a balance between performance area and energy efficiency.

Bit-serial processing, as a potential alternative, offers a simplified paradigm where data is executed one bit at a time. This approach has the potential to reduce power consumption due to its reduced hardware complexity and inherently sequential nature of execution. By exploring the feasibility of implementing bit-serial processing within the RISC-V ISA, this research aims to contribute to the growing body of knowledge in the area of energy and area-efficient microprocessor design.

### 1.4 Problem Statement and Contribution

The continued evolution of microprocessors now demands new innovative design approaches for energy-efficient and high-performance microprocessors. In the pursuit of making energy efficient computing solution the microprocessor designs tailored for low power applications has become vital. The conventional microprocessor designs which follow the parallel processing of instructions with increased complexity, lead to challenges in power consumption, area utilization, and manufacturing cost. In response to overcome these challenges, we need a design that resolve all these along with enough efficient in computing solutions. Hence the concept of bit-serial microprocessor design emerged as a potential solution. Which meets all these performance parameters.

Now the question that arises here is how it will be efficient in performance while maintaining these parameters. while bit-serial holds the promise of reduced power consumption and area utilization also it introduces new challenges regarding execution time and clock speed limitations. Therefore we have to accept the fact that we have to compromise on something to achieve something. In the bit-serial concept for achieving low power consumption, we have to compro-

### CHAPTER 1: INTRODUCTION AND MOTIVATION

mise a little on performance. But we can reduce this fact by making efficient designs and using multiple efficient solutions in a single design like bit-serial with pipe-lining.

# CHAPTER 2

# Literature Review

### 2.1 Microprocessor Architecture

The aim of this section is to provide you with an overview of the micro-architecture of conventional microprocessors which refers to the internal structure and design of a microprocessor, which serves as a central processing unit (CPU). It includes the phenomena that how the microprocessor carries out the instruction, memory management, and the communication of the microprocessor with slave devices. Remember that the architecture is a crucial factor in determining the performance, capability, and efficiency of a microprocessor. Micro-architecture is the implementation of Instruction Set Architecture (ISA). From Instruction fetching to the write back data in register file.

#### 2.1.1 Evolution of Microprocessors

A journey of continuous innovation and refinement in microprocessors. In Early eras, microprocessors were simple, single-core with limited computational power and large area. but with advancements in semiconductor technology, transistors became smaller and more efficient, allowing for the integration of multiple cores onto a single chip. This resulted in the transition of single-core microprocessors to multi-core microprocessors, enabling parallel processing and higher performance for tasks that could be divided among cores. Now the evolution has reached a point where we integrate not only a multi-core but multiple multi-cores in the same area using the latest bit-serial technique. Chapter 2: Literature Review

#### 2.1.2 Instruction Set Architecture (ISA)

Instruction set architecture is the language of the microprocessor. It provides the information about what the processor is capable of. It specifies the format of instruction, operations, and addressing modes. There are two commonly known ISAs RISC and CISC. RISC is a reduced instruction set computer and CISC is a complex instruction set computer. The choice of ISA influences the design and performance of a microprocessor, therefore choosing carefully and wisely.

#### 2.1.3 Data and Control Paths

As previously mentioned micro-architecture is the implementation of ISA, it involves two different paths to complete the circuit known as the control path and data path. Data path refers to the path through which data will moved from instruction memory to the decode stage then towards the execution unit to operate and then the memory and then the register file to write back the result. The control path is responsible for managing the flow of instructions including the branch prediction and jump to the instruction to be executed next. These components would work together to ensure the correct instruction execution.

#### 2.1.4 Instruction Execution

In early eras microprocessors were multi-cycled one instruction takes many cycles to be processed from fetching instructions to storing data. Then after a time, a technique named pipe-lined was introduced. Where we can process multiple instructions at a time. Hence the timing to process the instructions was reduced and throughput was increased. Pipe-line divides the microprocessor into different stages. Commonly it is divided into five stages as Instruction fetch, decode, execute, memory, and write back. But still, it's the designer's choice in how many stages he wants to divide its architecture.

### 2.2 Challenges in Microprocessor Design

Microprocessor design faces challenges such as clock skew, setup time violation, hold time violation, inferred latches, hazards, and non-hardware blocks. Therefore you have to stay focused when designing a microprocessor we have to keep in mind that each block would make

hardware. the block which will not make any hardware will not run after fabrication or on FPGA (Field Programmable Gate Array). For issues related to the clock, we have to properly divide the microprocessor into equal stages, and place the register or flip-flops clear fully so that not a single extra clock-edge cycle will be produced because a single extra clock cycle will disturb your complete design. We have to keep in mind that our pipeline cycle time will be equal to or greater than the critical path delay so that our instruction in each stage will process correctly without any timing violation.

# 2.3 Bit-Serial Execution

Bit-serial execution is a computational approach in which data is executed one bit per clockedge. Computations will be performed on individual bits. By reducing the hardware in contrast to increasing the execution time. This contrasts with parallel processing, where multiple bits or data elements are processed simultaneously. It implies that now we need just one operation block instead of several operation blocks. In conventional microprocessor designs where instructions are processed parallel thirty-two operation blocks are needed for thirty-two-bit instructions and likewise sixty-four blocks for sixty-four bits instructions. but in bit-serial design, just one operation block is used for either thirty-two bits or sixty-four bits instructions.

#### 2.3.1 Advantages and Limitations

#### Advantages:

- **Compact Design:** Bit-serial microprocessors often have compact and simpler designs due to their serial execution nature which can lead to smaller size and low manufacturing cost.

- Parallelism: Due to its serial nature it has a lower rate of throughput than conventional

parallel microprocessors, but we can increase it by introducing parallelism nature in bitserial microprocessors. When a microprocessor becomes parallel multiple stages work on

the same clock edge and different instructions are processed in different stages at the same

time which can lead to higher throughput.

- Low Complexity: Bit-serial microprocessor has lower complexity than a conventional parallel microprocessor because the data path is now reduced from thirty-two bit to one bit. Also it simply the arithmetic and logic unit from thirty-two to one bit which can lead to easier chip layout due to lower transistor count.

- **Reduced Interconnects:** Due to the bit-serial nature of microprocessor design it requires less interconnect between processing elements the conventional parallel microprocessors which can improve overall performance due to lower signal delay.

- **High Clock Frequencies:** Bit-serial nature can allow us for higher clock frequency since the complexity of processing is now one bit which is lower than processing a whole word,

#### Limitations:

- Limited Data Width: bit-serial microprocessor can handle only one-bit data which can lead to slower processing for an operation that requires a large data path such as complex arithmetic and memory access.

- **Complex instructions :** Operations that can combine multiple bits can be complex and leads microprocessors to additional pipeline stages which can lead to increased latency.

- Software Challenges: Bit-serial nature of microprocessors often requires specialized programming techniques to take full advantage of their architecture. which can limit the portability of software and make it more difficult to optimize the code.

- Performance Trade-offs: While bit-serial microprocessor design can achieve higher clock frequency, the performance gains might not always be proportional to conventional parallel microprocessors due to the higher execution latency and additional pipeline stages that will required for more complex operations.

- Limited Applicability: Bit-serial pipelined microprocessors are better suited for specific types of workloads, such as signal processing and certain forms of cryptography. They might not be as effective for general-purpose computing tasks as conventional parallel microprocessors.

- Bit-Level Operations: Performing operations at the bit level can introduce additional overhead for certain tasks that could be more efficiently handled by using wider data paths in traditional microprocessors.

- Complex Hardware: The design and implementation of bit-serial microprocessors can be complex, especially when dealing with operations that require multi-bit manipulation or inter-bit dependencies.

## 2.4 RISC-V Instruction Set Architecture

As mentioned earlier ISA is the language of any microprocessor. Therefore always choose wisely. We choose RISC-V ISA due to its open source and extensible nature. And also it is easy in micro-architecture. It has three types of operations. [1] Register file to Register file. [2] Register file to memory. [3] control flow, to jump on different addresses or instructions.

- It has seven seven-bit opcodes to specify the type of instructions.

- It has a small and fixed amount of registers.

- · Each register has a bit address which can lead up to thirty-two registers.

- Three bits to address which function to be performed are named funct3.

- Seven bits to differentiate between the operations whos have the same funct3 bits.

- And it has a variable amount of immediate based on the type of instructions.

| 31:25        | 24:20           | 19:15 | 14:12  | 11:7        | 6:0    | Format |

|--------------|-----------------|-------|--------|-------------|--------|--------|

| Funct7       | Rs2             | Rs1   | Funct3 | Rd          | Opcode | R      |

| Imm[11:      | 0]              | Rs1   | funct3 | Rd          | Opcode | I      |

| Imm[11:5]    | Rs2             | Rs1   | Funct3 | Imm[4:0]    | Opcode | S      |

| Imm[12 10:5] | Rs2             | Rs1   | Funct3 | Imm[4:1 11] | Opcode | В      |

|              | Imm[31:12]      |       |        | Rd          | Opcode | U      |

| Imm          | n[20 10:1 11 19 | :12]  |        | Rd          | Opcode | J      |

Table 2.1: RISC-V ISA.

# Chapter 3

# Design and Methodology

While designing a microprocessor we were implementing the ISA (Instruction Set Architecture). In our design, we implemented the RISC (Reduced Instruction Set Computer) ISA. And before go onto actual design lets concise the RISC-V ISA first. As mentioned earlier it has three types of operations.

- Register file to Register file.

- Register file to Memory.

- Control flow.

But there are a lot more in ISA. It has six types of instructions and also it has three different type of addressing modes. let's discuss these one by one.

## 3.1 Types of Instructions

- R: These are Register file to Register file type operations. Contains two source registers and a destinations register.

- I: These are also Register file to Register file operations, but in these instructions, one operand is source register one and second operand will be immediate/offset value and the third operand will be destination register. But in these types of operations, one instruction is a little different **JALR** it uses a combination of Register file to Register file and control flow operation. it stores the address of the current instruction in the destination register and also jumps to the next instruction.

- S: These are register files to Memory type operations these have one source register and an immediate/offset value and the source register two. Source register two is the data that will be stored in Memory.

- U: These are Register file to Register file operations but they have destination register and an immediate/offset value instead of using source register one or two they used the address of current instruction.

- J: It is a combination of Register file to Register file and control flow operations. It has one destination register and like U type instructions they used the address of the current instruction instead of the source register one or two. The address of the current instruction will be stored on the destination register and also it calculates the address of the next instruction.

- B: These are pure control flow instructions. These include two source registers, which are used for operation and based on their result processor will jump on the next address/instruction.

## 3.2 Addressing Modes

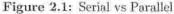

1. **PC-Relative:** Type of addressing mode used in RISC-V ISA. In this mode, the effective memory address of the next instruction is calculated as an offset using the address of the instruction that is currently being executed.

PC-relative addressing mode is commonly used for control flow or branching instruction. where the target address of instruction is relative to the address of current instruction. This mode is particularly useful for conditional and unconditional branching, as it allows the efficient encoding of small offsets in this type of instruction format.

#### How it works?

Immediate Decoding: As I mentioned earlier it has two source registers two immediate/offset values and a funct3 bits to specify the function type. The notable point in this format is that we have to carefully entertain the offsets of this instruction and carefully decode them using proper decoding against the offset encoding.

Imm[4:1|11] represents that the seventh bit of instruction is the eleventh bit of Immediate, and the rest of the bits from eight to ten bits of instructions are one to Chapter 3: Design and Methodology

fourth bits of Immediate.

Imm[12|10:5] same in this twenty-five to thirty bits of instructions are five to ten bits of an immediate, and thirty-first bit of instruction is a twelfth bit of immediate.

• Calculation: when instruction is executing based on the comparison result of instruction Program counter will incremented. if the comparison result is true then the address of the current instruction in the execute stage will add with the offset value of the current instruction and then the program counter will jump to that address else the program counter will be incremented as usual by adding four to the current address in the program counter. Note that for jump the offset and address that will used is of the instruction presented in the execute stage.

PC-relative addressing mode is only advantageous because it reduces the size of instructions in memory, as only the immediate need to be stored instruction. Especially beneficial for RISC architecture because it has a smaller and typically fixed size of instruction. A limitation of the Pc-relative addressing mode is that it is only beneficial for short-range branching/jumping. because a large offset needs more bits which typically increases the size of instruction

In summary, PC-relative addressing mode is a key mechanism in RISC ISAs for efficient branching/jumping and control flow instructions by using immediate/offset relative to the Program Counter, contributing to the overall speed and simplicity of RISC architectures.

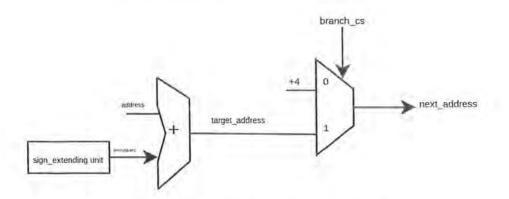

2. Register Offset: addressing mode sometimes refer as "register plus" or "register index" addressing mode. Commonly used in computer architecture including RISC architecture. in this addressing mode effective memory address will be calculated by adding the immediate/offset with the data specified by one of the source operand registers of instruction. This addressing mode is often used inLoad/Store instruction for accessing the data memory,

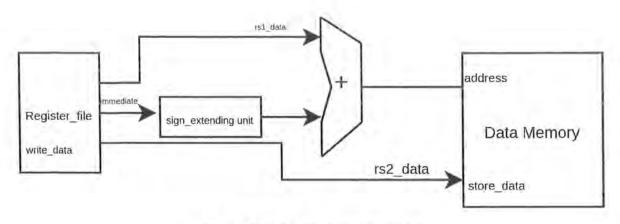

Figure 3.1: Conventional Parallel Branching

#### How it works?

- Immediate Decoding: There are two types of instructions format I and S that use this type of addressing mode. let's discuss it one by one

- (a) Load Immediate Decoding: It has a simple twelve bits offset presented all bits together from twenty fifth bit to thirty-first bit of instruction. you have to just sign and extend it to thirty-two bits to decode it.

- (b) Store Immediate Decoding: Carefully observes the arrangement of the bit then seven to eleven bits of the instruction are the first four bits of immediate/offset. then the twenty-fifth to thirty-first bits are the rest bits. for decoding care fully arrange these bits then sign extend these bits up to 32 bits.

- Calculation:

- (a) Load Address Calculation: for Load instruction we have to add the data located at the address of the source register with the sign-extended immediate/offset presented in the twelve MSB (Most Significant Bits) bits of instruction to make the target address for data memory.

- (b) Store Address Calculation: for Store instruction we have to first arrange the offset/immediate presented in the different bits of instruction the sign extends it up to thirty-two bits then adds it with the data located at the address of the source register one to get the target address of data memory.

**Note:** The question arises here then what will be the purpose of the source register two here?

The answer for that is the data located at the address of source register two is the data to be stored in memory.

Register offset address mode is beneficial because it gives us the flexibility of accessing memory without requiring separate load and store instructions, for different addressing modes such as a store, load byte or store, load half word or store, load word. Also it has the advantage that using register offset addressing mode we can access a large number of location inside the data memory, without the need of any extra bits. But! how much there for it has limitations based on the bits of source operand data and immediate bits. There for we can access the large number of locations but also a limited number of locations.

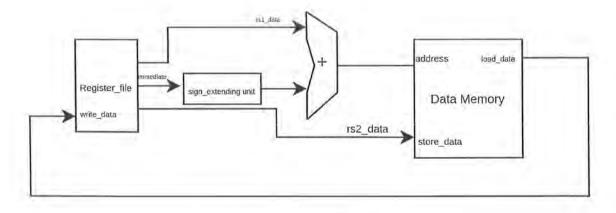

Figure 3.2: Parallel Load Instruction

3. Absolute Addressing: In absolute addressing mode, the memory address of a data or operand is directly specified within the instruction itself. The instruction contains the exact memory location where data should be stored or from where data should be fetched. Also, one of the instructions is named Lui (Load Upper Immediate) this instruction contains data itself that should be stored in the destination register. In this Instruction no extra logic is needed we just assign the data to the destination register directly. In other instructions we calculate data as its types as discussed earlier the only difference

Figure 3.3: Parallel Store Instruction

is that we don't need any extra logic for targeted source register or memory location we just use the immediate/offset of instruction and calculate the address or data directly.

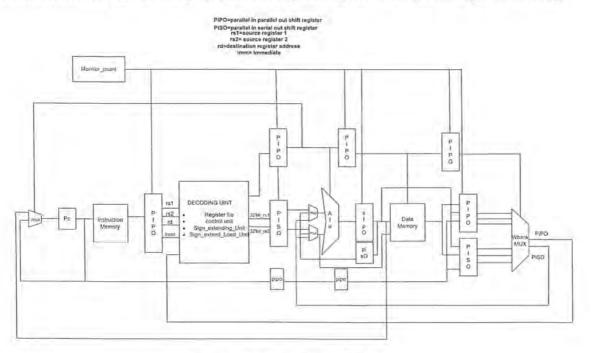

# 3.3 Architectural Overview

The bit-serial microprocessor has a single-bit microarchitecture, processing/executing instructions one-bit per clock edge rather than executing a whole word or byte like conventional parallel microprocessors. It operates on a single bit sequentially. Bit-serial microprocessor follows the same ISA as conventional microprocessors but still, it has a different microarchitecture, due to their serial nature. its data path is single-bit wide.

The data path for the fetch and decoding stages are the same as conventional parallel microprocessors the difference in the data path started after the decoding stage. before the decoding stage, it has thirty two bit wide data path but after the decode stage data path is converted from thirty-two to one-bit wide. Bit-serial microprocessor required 34 clock-edges at each stage to process the thirty-two-bit instructions. Two cycles overhead is to handle the data dependencies. let's discuss the main architectural components in each stage one by one.

- 1. Fetch Stage Used to fetch the instruction from Imem(Instruction Memory). It contains two main components.

- **Program Counter:** one input and one output, used to assign the memory address to Instruction Memory, based on the mux output connected with the input of the program counter. The program counter either assigns the incremented by four or

Chapter 3: Design and Methodology

plus four (+4) address or it assigns the next targeted address calculated by branch or jump instructions.

- Instruction Memory: one input one out, contains pre-stored instructions. Used to assign the instructions to the microprocessor's decoding unit based on the address assigned by the program counter.

- 2. Decode Stage it takes the thirty-two bits instruction from instruction memory and decode it's all operands, and assign to their destinations, it includes

- Register File: Five inputs and two outputs, addresses of source registers and destination register are input and are assigned to register file after decoding from instruction. Write enable signal and write data are also inputs to the register file. The register file provides the data located on the source register address to the execution unit.

- **Control Unit:** It takes the seven-bit opcode and three bits of funct3 and seven bits of funct7 from the instruction then makes the data and control signals based on the opcode, funct3 and funct7 of instruction, which helps to control the data path of the microprocessor.

- Sign Extending Unit: take the immediate/offset as input and sign extend it to the thirty bits. As you observed in ISA different instructions have different bits of immediate/offset but remember microprocessor will operate on fixed defined bits if the microprocessor is thirty-two bit then it processes all data on thirty-two bits, and the same as for 16 or sixty-four bits. therefore we extend the immediate/offset to thirty-two bits.

- Load Unit: use to sign extend the resultant data after loading from data memory. As we have different types of load instructions such as Lh(Load half) or Lb(load byte) there for before storing it in the destination register we have to extend it up to thirty-two bits.

- Alu Decoder: make the operation control bits for execution unit ALU (Arithmetic Logic Unit) based on instruction.

- 3. Execute Stage Contain only one component,

- Alu(Arithmetic Logic Unit): perform the operation based on the operation control unit assigned by the alu decoder.

- 4. Memory Stage It contain two component,

- Data Memory: take alu output as the address of location and data located as a source register two as data to be stored.

- Store Unit: used to build the byte enable for data memory. based on which data will be stored on the specific bits at the located address.

- 5. Write Back Stage only contains a mux for selecting the data that will be stored on destination register.

### 3.4 Bit-Serial Data Path Design

It's clear from the name bit-serial that the whole data path will be one bit wide, but in our design not the whole data path will be one bit wide, As our design in pipelined there for our data path is the same as conventional parallel microprocessor data path till decode stage. The serial data path will start after the decode stage, this is to avoid the multi-cycle phenomena in pipelined microprocessor.

Note that we can not fetch instruction one bit per clock edge from instruction memory and also can not decode the instruction on one bit per clock edge to obtain this format we have to convert an instruction from whole word to bit stream and then convert the bit stream into whole word to decode the instruction which implies the multi-cycle phenomena in decode stage. Likewise, after the write back stage, we can not store the bit stream in the destinations register one bit per clock edge there for we have to convert the bit stream into a complete word to write it back.

Therefore when designing a bit-serial data path, we have to convert the conventional data path that is thirty-two bit wide into one bit wide data path there for now in the bit-serial data path all the components that are designed to process the thirty-two bits word are now design to process the bit stream that will be one-bit per-clock-edge. Two Key components helps us to design the bit-serial data path.

• **Counter:** responsible to to count the bits and to monitor the each stage to active for required cycles to process the instruction. In our Design it will count up to thirty four cycles, to process the thirty two bits instructions, which means each stage is activate for thirty four cycles, to process the instruction.

- Shift Register: It is an Heart of bit-serial data path. used to convert the thirty two bit word into a bit-stream, to process one bit per-clock-edge. Two types of Shift Registers are used in our Design

- Parallel-In-Serial-Out (PISO) Shift Register: take thirty-two bit word as input and convert it into a bit-stream of thirty-two bits. In PSIO Shift register we have two types of shift rigters,

- (a) MSB to LSB PSIO Shift Register: it take thirty two bit word as input and convert into bit stream that will starts from MSB (Most Significant Bit) end at last gave us LSB(Least Significant Bit).

- (b) LSB to MSB PSIO Shift Register: It's output starts from LSB (Least Significant Bit) and ends at MSB(Most Significant Bit).

- Serial-In-Parallel-Out (SIPO) Shift Register: it take the thirty bit stream of thirty two bits and combine it in a thirty two bits word. Like PSIO we used two types of SIPO registers.

- (a) LSB First: it takes LSB first and MSB at last.

- (b) MSB First: it takes MSB first and LSB at last.

As we discuss the key components of bit-serial microprocessor, now lets discuss some important components is serial manner. As in our design serial data path will start after decode stage therefor the first components will be

(a) Arithmetic and Logic Unit (ALU): in serial manner alu will be one bit wide there for the input should be one bit wide, in bit-serial we have one block for each operation, instead of using thirty two block like in conventional parallel microprocessor. For this purpose we have to convert the thirty two bit word into a bit stream and for this we used sift registers like PISO or SIPO based on instructions. As in conventional microprocessor instructions are executed in one clock cycle but in bit-serial microprocessor instructions will be execute in thirty two clock cycles, because data width is thirty two bits and operation will perform on each individual bit, there for in bit-serial data path ALU will be activated for thirty two clock cycles.

**Note:** In our design of bit-serial alu most of the instructions are executed using addition block.

Here question rises how ? we will discuss it in implementation chapter.

- (b) Data Memory (DMem): as i mentioned earlier we can not access data memory using serial bit, we need complete thirty two bits word to access the memory. there for we convert the alu result which will be the address of data memory and rs2\_data which will be the data that will stored in dmem, from bit stream to a complete word, for this purpose we will use SIPO shift register.

- (c) Write Back Mux: as write aback mux used for two purpose one is to write back the data in register file, second is to handle the hazard there for in bit-serial we used two type of write back muxes

- Parallel in Parallel Out Mux: for write back purpose.

- Parallel in Serial Out Mux: for handling the hazards, to forward the data towards alu.

# 3.5 Design Consideration for Energy Efficiency

This section involves the techniques that we use to make our design suitable for low power applications with high efficiency.

Note: that when we improving one factor we have to compromise on other factor to gain some thing we have to lose some thing. As our main goal is to make our design suitable for low power application there for we have to compromise a little bit on through put (Efficiency). we use two techniques.

#### 3.5.1 Serial Execution:

we make our design bit-serial which means in our design instructions will executed serially onebit per-clock-edge. operation will perform on each individual bits. which will make our design smaller then conventional parallel microprocessor design. and as the area is reduced power will automatically be reduces because the number of components in design is reduced.

in conventional microprocessor design each operation will use thirty two operation block to execute instruction in one clock edge which will used huge area. and each operation will have different blocks. Such as "shift left, shift right, comparison, subtraction, addition" each operation will required different operation block and each operations have different voltage level. In contrast with this our design will used single operation block of Addition for most of instruction and as we observe from thirty two parallel block to one block area will reduce with

large number.

Now lets do a rough comparison,

| Operation<br>Blocks | Parallel | Serial |

|---------------------|----------|--------|

| Addition            | 32       | 1      |

| Subtraction         | 32       | 1      |

| Right Shift         | 32       | 1      |

| Left Shift          | 32       | 1      |

| Less then           | 32       | 1      |

| Greater Then        | 32       | 1      |

| Total               | 192      | 1      |

Table 3.1: Operation count Parallel vs Serial.

As you can see that in just a rough calculation where in conventional parallel design number of operation blocks are 192 and in serial its only one, and these are only six operation from thirty two operations and difference in numbers is huge and if we make a supposition,

Suppose one operation blocks consume 1nm area then for these operations 192nm area will required for parallel design and only 1nm are is required for serial design.

this difference is only for counted operation in just ALU which is only one component of microprocessor, now just imagine area required for muxes registers and all other components that are thirty two bit wide in parallel design. Now imagine how much area will be reduced by making it serial. And power that will be required for 192 components is reduce to only for one component. Suppose if one block use 1mv then 192mv for parallel design and only 1mv for serial design.

#### 3.5.2 Instruction Pipelining

As i said earlier to achieve some thing we have to lose some thing, there for in our design we lose the efficiency because the instruction that will execute in one clock cycles will now execute in thirty two clock cycles hence time for execution is increased in contrast the through put is decreased.

To over come this issue we make our Design pipe-lined. As in no-pipelined design the only one instruction will process on thirty two clock cycles but now in pipelined design the five different instructions will process in same thirty two clock cycles because we divide our design oin five Chapter 3: Design and Methodology

different stages using pipelining. hence throughput will increased from one to five.

# CHAPTER 4

# **Implementations Details**

This chapter includes the detail explanation regarding how the ISA was implemented using bitserial and pipelining technique. We will discuss all three types of operations and the instructions under these types, with complete microarchitecture and data path.

# 4.1 Pipelining